ADSP-21368 SHARC Processor Hardware Reference A-35

Register Reference

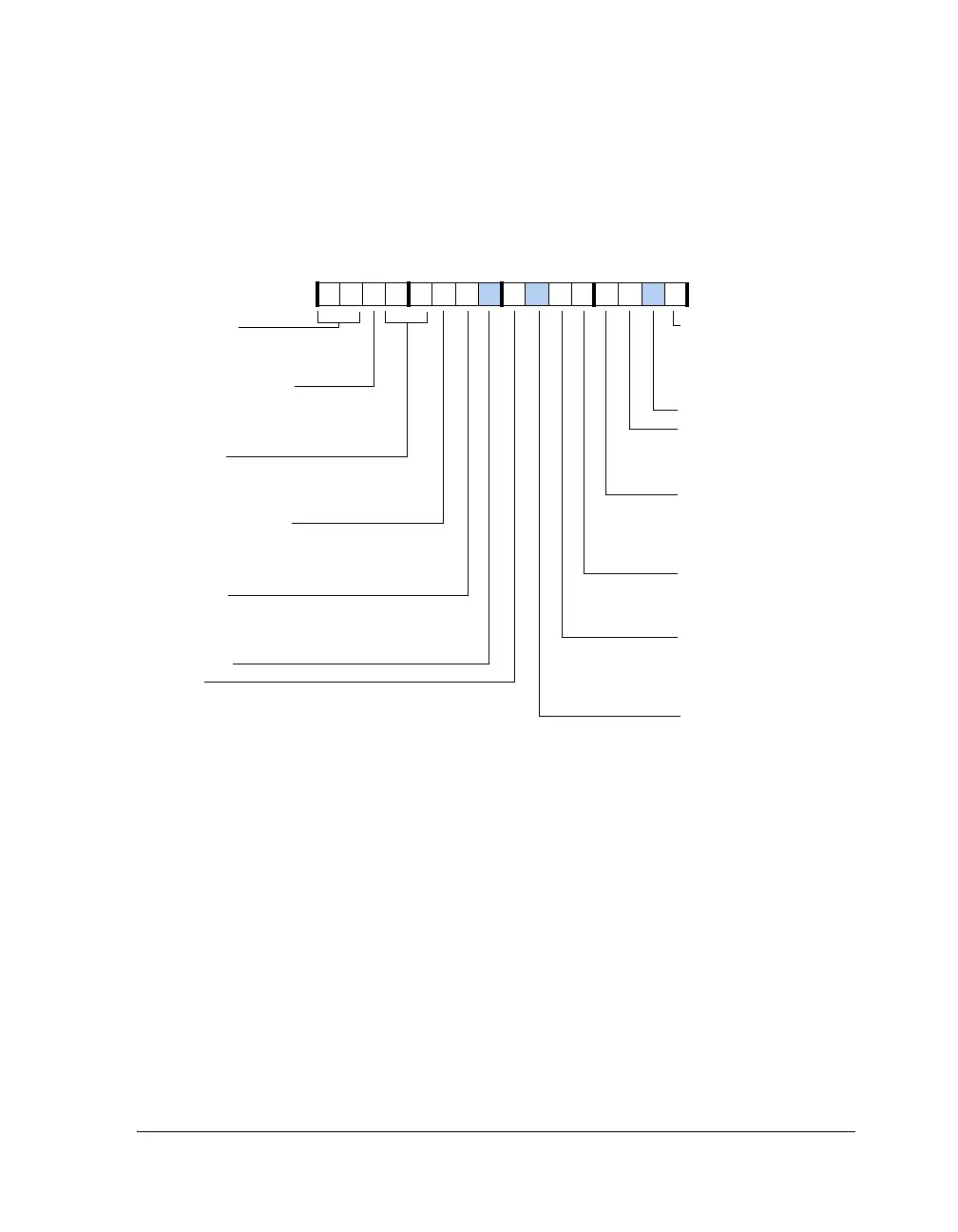

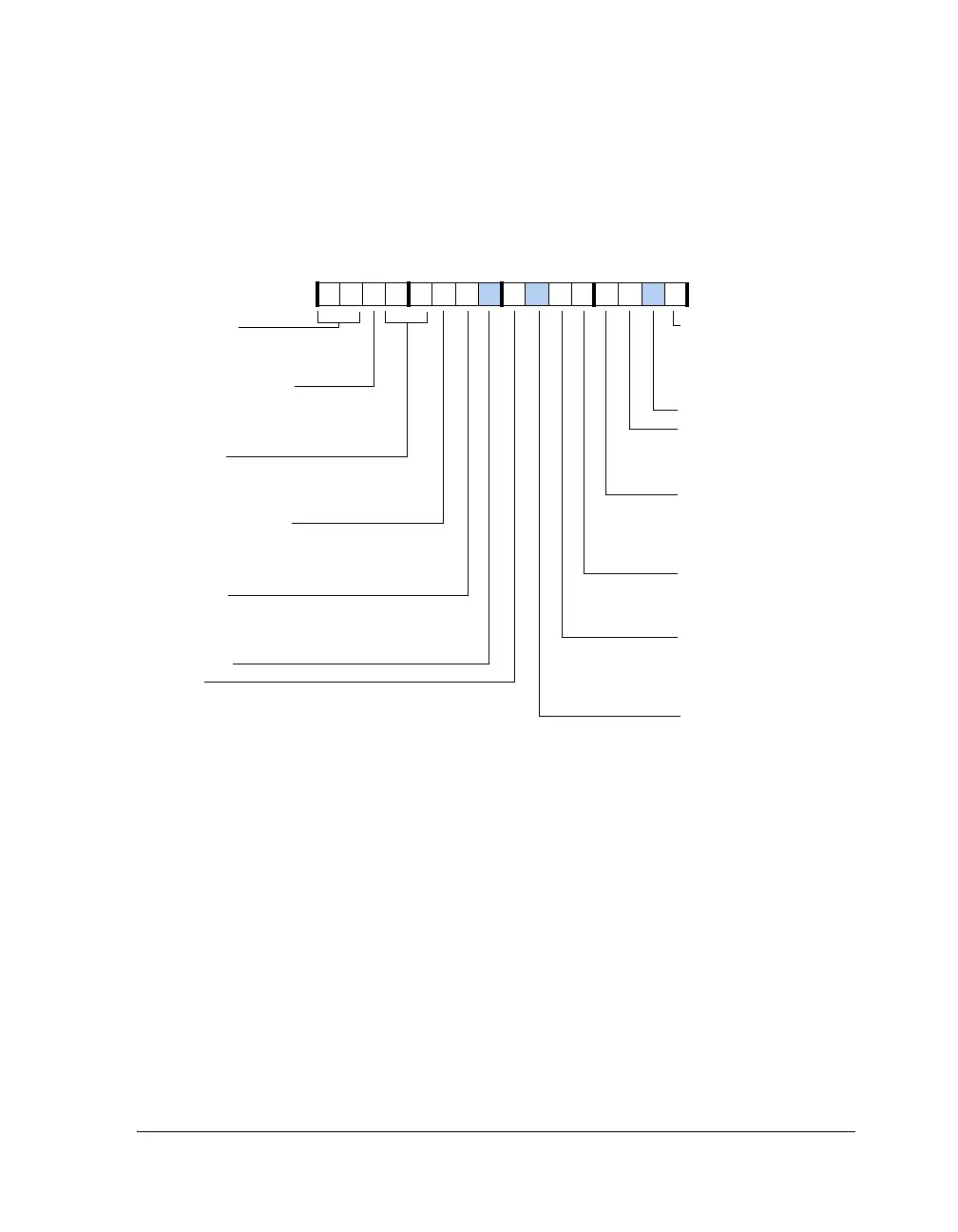

Figure A-17. SPCTLx Register (Bits 31–16) for Packed I

2

S and

Multichannel Mode

31 30 29 28 27 26 24 23 22 21 20 19 18 17 16

00000000000 00000

DXS_A

Data Buffer Channel A Status

11=Full 10=Partially full 00=Empty

LMFS

Active Low Multichannel Frame

Sync

1=Active low FS

0=Active high FS

DERR_A (TUVF_A or

ROVF_A)

Channel A Error Status (sticky)

SPTRAN=1 Transmit underflow status

SPTRAN=0 Receive overflow status

SDEN_A

Receive DMA Channel A Enable

1=Enable

0=Disable

DXS_B

Data Buffer Channel B Status

11=Full 10=Partially full 00=Empty

BHD

Buffer Hang Disable

1=Ignore core hang

0=Core stall when TXn full or RXn empty

SCHEN_A

Receive DMA Channel A

Chaining Enable

1=Enable

0=Disable

SDEN_B

Receive DMA Channel B Enable

1=Enable

0=Disable

SCHEN_B

Receive DMA Channel B Chaining

Enable

1=Enable

0=Disable

Reserved

Reserved

25

SPTRAN

SPORT Data Direction

1=Transmit

0=Receive

SPCTL0 (0xC00) SPCTL1 (0xC01)

SPCTL2 (0x400) SPCTL3 (0x401)

SPCTL4 (0x800) SPCTL5 (0x801)

SPCTL6 (0x4800) SPCTL7 (0x4801)

DERR_B (TUVF_B or

ROVF_B)

Channel B Error Status (sticky)

SPTRAN=1 Transmit underflow status

SPTRAN=0 Receive overflow status

Reserved

Loading...

Loading...