Serial Port Registers

A-42 ADSP-21368 SHARC Processor Hardware Reference

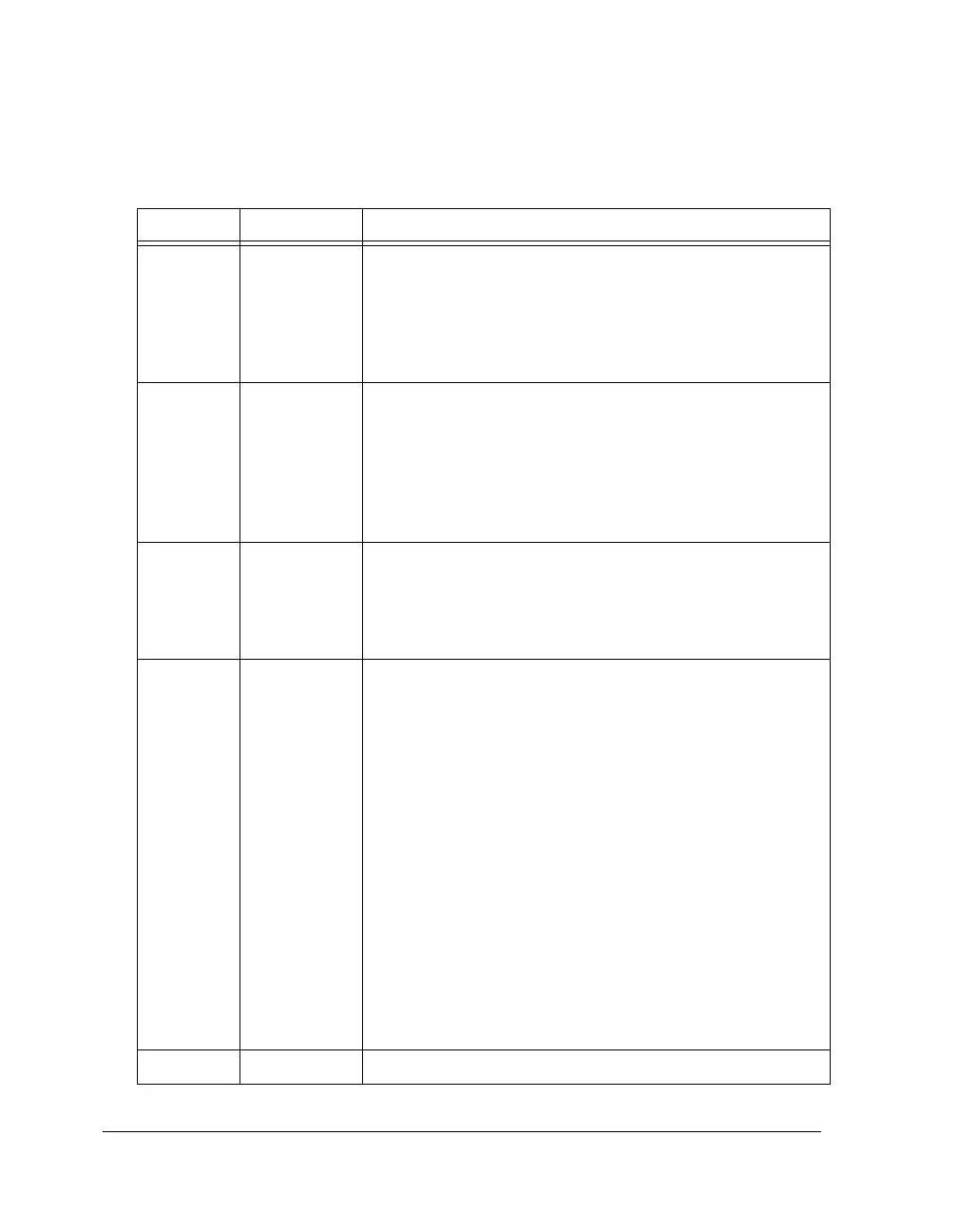

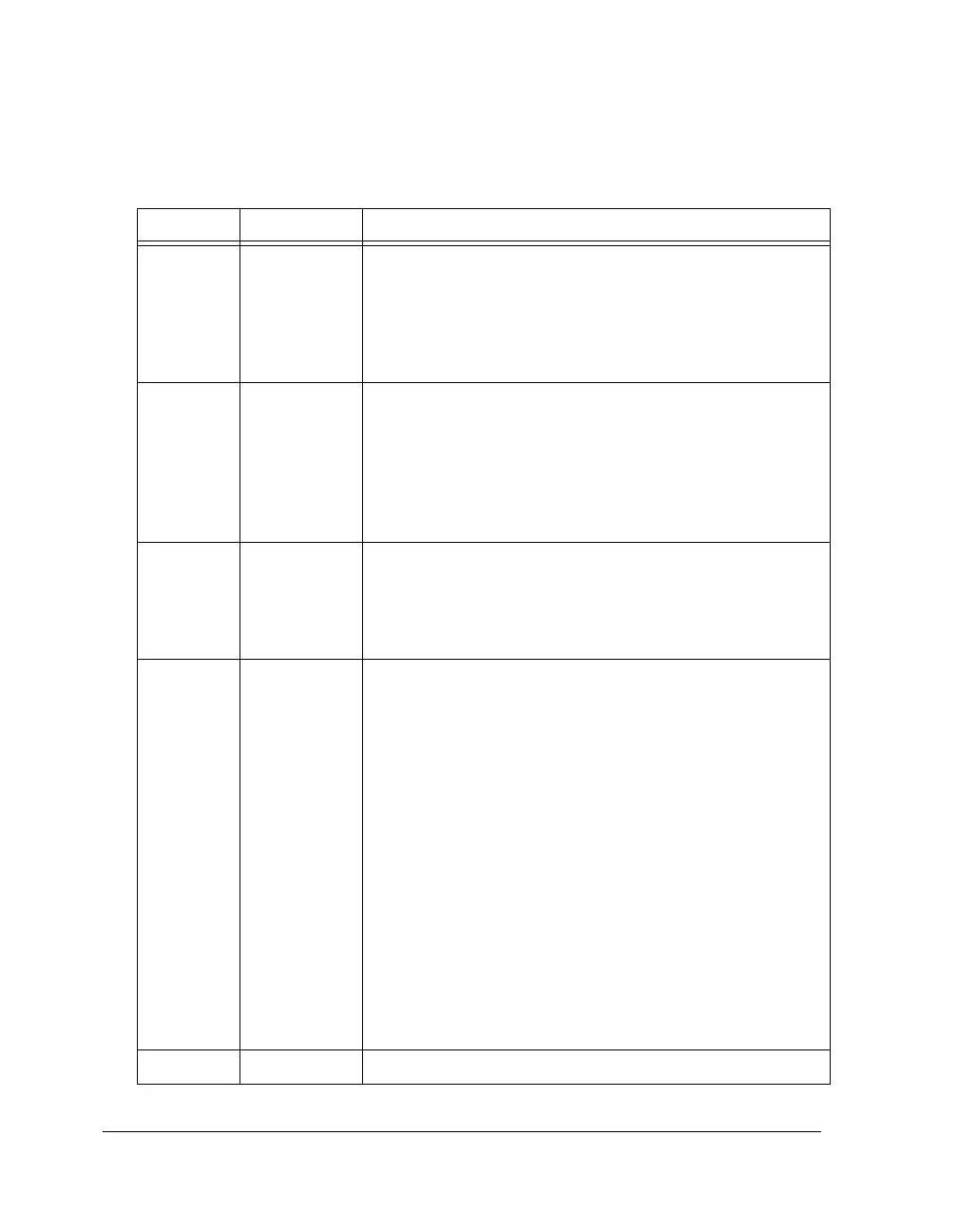

Table A-9. SPMCTLx Register Bit Descriptions

Bit Name Description

0MCEAMultichannel Mode Enable. Standard and multichannel modes

only. One of two configuration bits that enable and disable mul-

tichannel mode on serial port channels. See OPMODE bit

on page A-37.

0 = Disable multichannel operation

1 = Enable multichannel operation if OPMODE = 0

4–1 MFD Multichannel Frame Delay. Set the interval, in number of serial

clock cycles, between the multichannel frame sync pulse and the

first data bit. These bits provide support for different types of T1

interface devices. Valid values range from 0 to 15 with bits [4:1].

Values of 1 to15 correspond to the number of intervening serial

clock cycles. A value of 0 corresponds to no delay. The multi-

channel frame sync pulse is concurrent with first data bit.

11–5 NCH Number of Multichannel Slots (minus one). Select the number

of channel slots (maximum of 128) to use for multichannel oper-

ation. Valid values for actual number of channel slots range from

1 to 128. Use this formula to calculate the value for NCH:

NCH = Actual number of channel slots – 1.

12 SPL SPORT Loopback Mode. Enables if set (= 1) or disables if

cleared (= 0) the channel loopback mode. Loopback mode

enables developers to run internal tests and to debug applications.

Loopback works under the following SPORT configurations

where either of the two paired SPORTs can be set up to transmit

or receive, depending on their SPTRAN bit setting.

SPORT0 and SPORT1. SPORT0 can only be paired with

SPORT1, controlled by the SPL bit in the SPMCTL0 register.

SPORT2 and SPORT3. SPORT2 can only be paired with

SPORT3, controlled by the SPL bit in the SPMCTL2 register.

SPORT4 and SPORT5. SPORT4 can only be paired with

SPORT5, controlled by the SPL bit in the SPMCTL4 register.

SPORT6 and SPORT7. SPORT6 can only be paired with

SPORT7, controlled via SPL bit in the SPMCTL6 register

15–13 Reserved

Loading...

Loading...