Serial Peripheral Interface Registers

A-54 ADSP-21368 SHARC Processor Hardware Reference

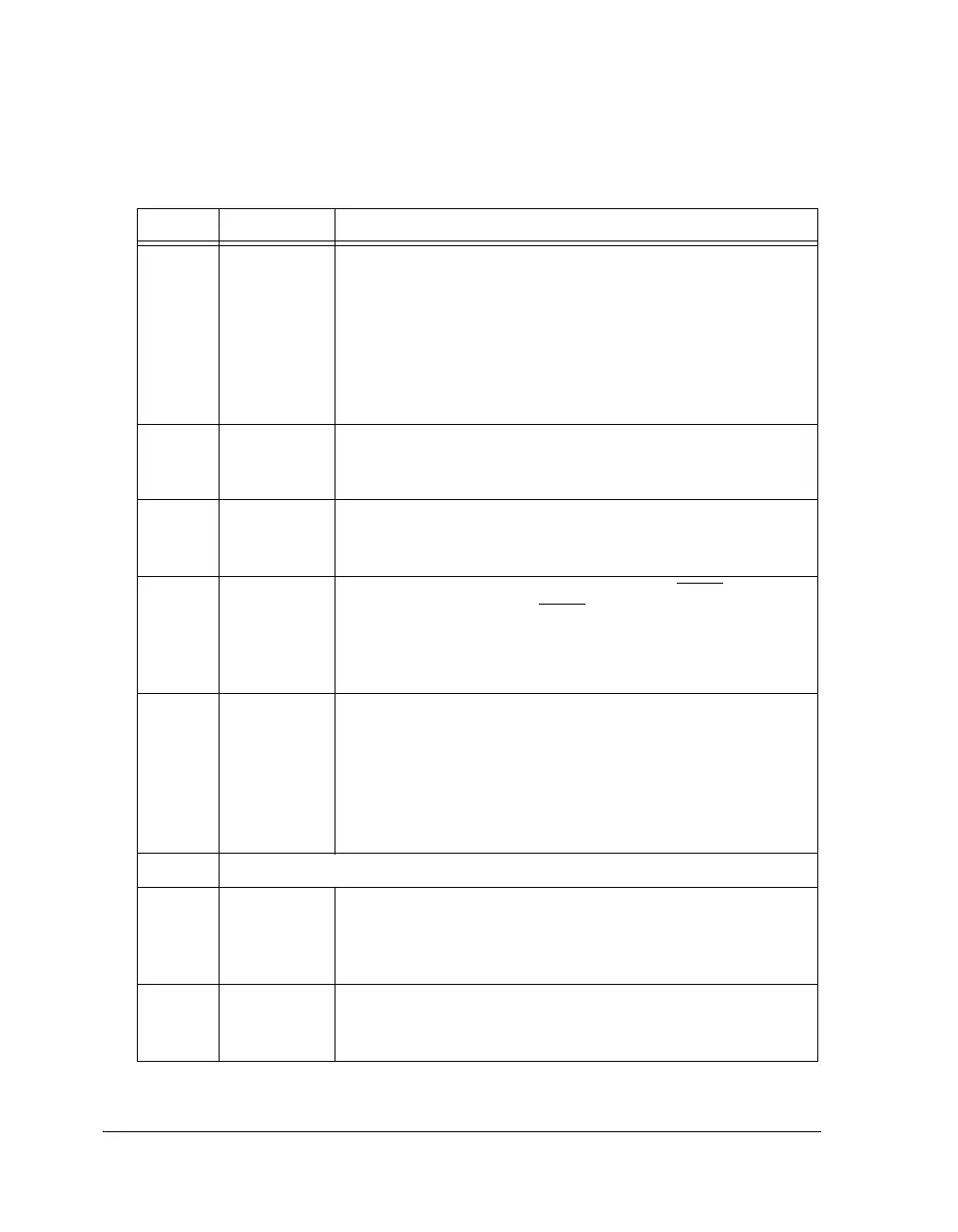

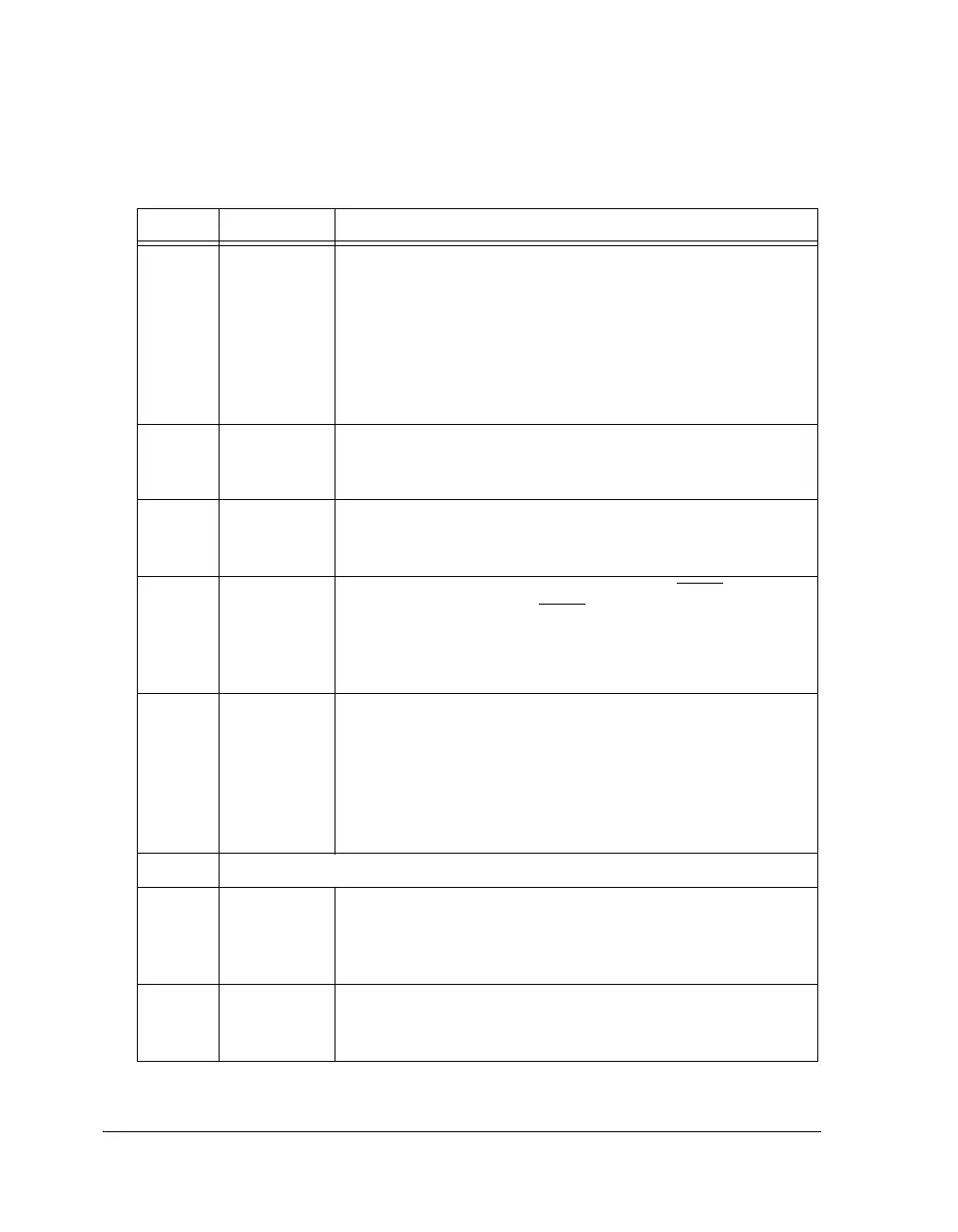

Table A-10. SPICTL Register Bit Descriptions

Bit Name Description

1–0 TIMOD Transfer Initiation Mode. Defines transfer initiation mode and

interrupt generation.

00 = Initiate transfer by read of receive buffer. Interrupt active when

receive buffer is full.

01 = Initiate transfer by write to transmit buffer. Interrupt active

when transmit buffer is empty.

10 = Enable DMA transfer mode. Interrupt configured by DMA.

11 = Reserved

2SENDZSend Zero. Send zero or the last word when TXSPI is empty.

0 = Send last word

1 = Send zeros

3GM Get Data. When RXSPI is full, get data or discard incoming data

0 = Discard incoming data

1 = Get more data, overwrites the previous data

4ISSENInput Slave-Select Enable. Enables slave-select (SPIDS

) input for

the master. When not used, SPIDS

can be disabled, freeing up a

chip pin as a general-purpose I/O pin.

0 = Disable

1 = Enable

5DMISODisable MISO Pin. Disables MISO as an output. This is needed in

an environment where a master wishes to transmit to various slaves

at one time (broadcast). However, only one slave is allowed to trans-

mit data back to the master. This bit should be set for all slaves,

except the one from whom the master wishes to receive data.

0 = MISO enabled

1 = MISO disabled

6Reserved

8–7 WL Word Length.

00 = 8 bits

01 = 16 bits

10 = 32 bits

9MSBFMost Significant Byte First.

0 = LSB sent/received first

1 = MSB sent/received first

Loading...

Loading...