ADSP-21368 SHARC Processor Hardware Reference A-53

Register Reference

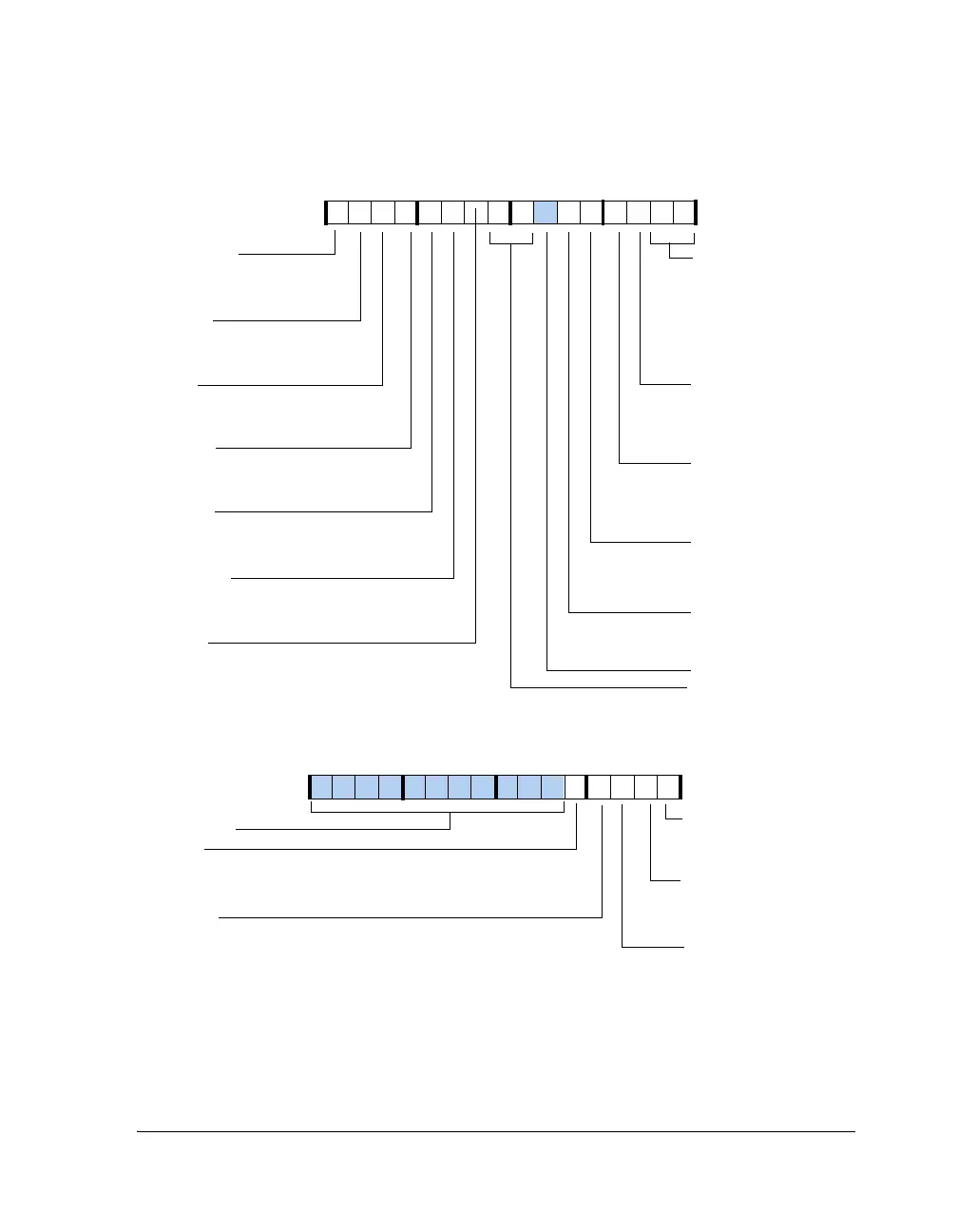

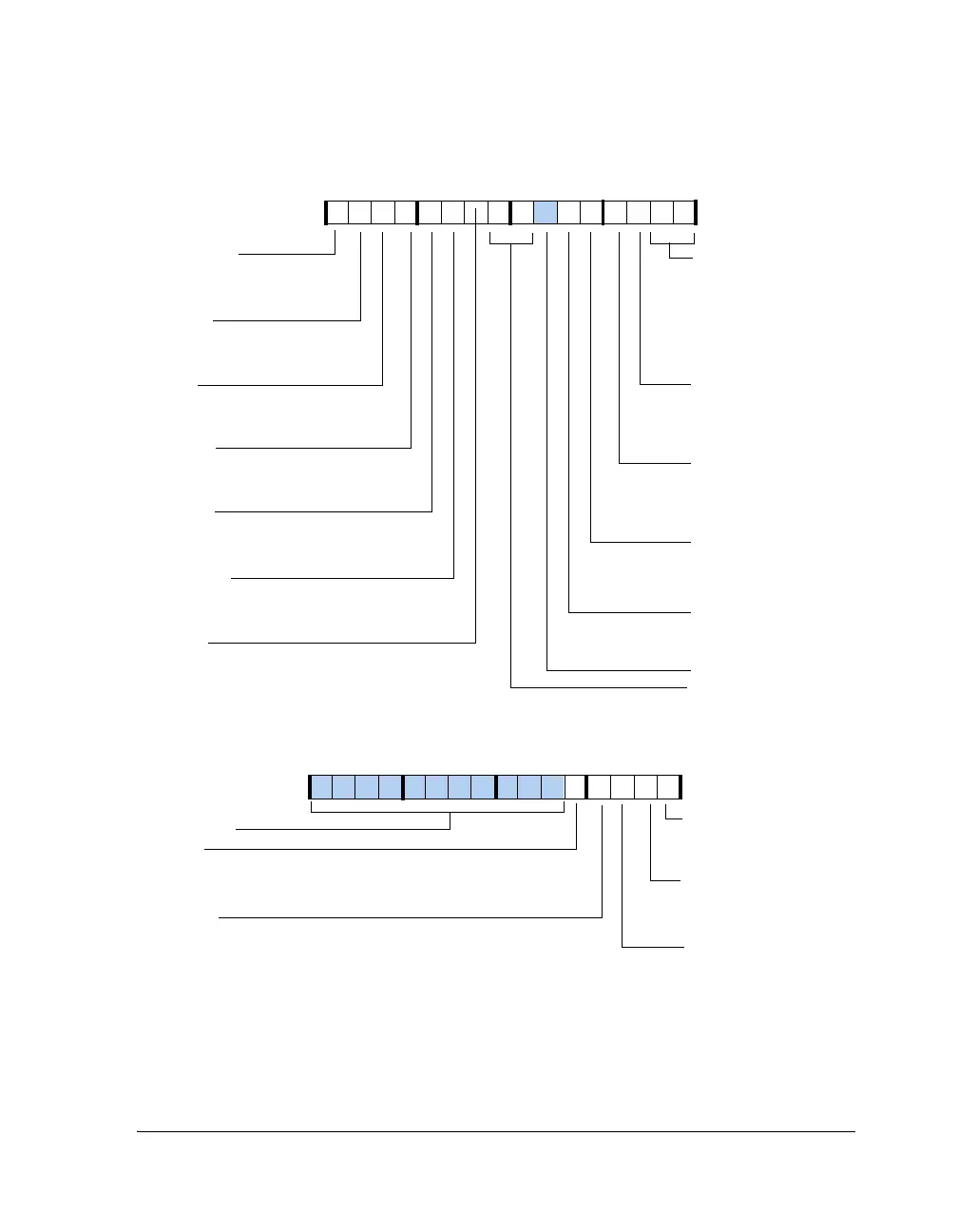

Figure A-23. SPICTL, SPICTLB Registers

15 14 13 12 11 10 8 7 6 5 4 3 2 1 0

0000000000000000

PACKEN

TIMOD

Transfer Initiation Mode

00=Initiate transfer by read of

receive buffer

01=Initiate transfer by write of

transmit buffer

10=Enable DMA transfer mode

11=Reserved

Reserved

8-Bit Packing Enable

1=8- to 16-bit packing

0=No packing

SPIEN

SPI System Enable

1=Enable

0=Disable

OPD

Open Drain Output Enable for Data Pins

1=Open drain

0=Normal

SPIMS

Master Slave Mode Bit

1=SPI master device

0=SPI slave device

CLKPL

CPHASE

MSBF

Most Significant Byte First

1=MSB sent/received first

0=LSB sent/received first

SENDZ

Send Zero or Last Byte

when SPITX Empty

1=Send zeros

0=Send last word

GM

Fetch/Discard Incoming Data

when SPIRX Full

1=Overwrite with new data

0=Discard incoming data

ISSEN

Input Slave Select Enable

1=Enable

0=Disable

DMISO

Disable MISO Pin (Broadcast)

1=MISO disabled

0=MISO enabled

WL

Word Length

00=8 bits, 01=16 bits,

10=32 bits, 11=Reserved

9

SPICTL (0x1000)

SPICTLB (0x2800)

Clock Polarity

0=Active high SPICLK (low is the idle state)

1=Active low SPICLK (high is the idle state)

Clock Phase

0=SPICLK toggles at middle of 1st data bit

1=SPICLK toggles at start of 1st data bit

31 30 29 28 27 26 24 23 22 21 20 19 18 17 16

0000000000000000

Reserved

SGN

Sign Extend Data

1=Sign extend

0=No sign extend

SMLS

Seamless Transfer

1=Enable

0=Disable

TXFLSH

Transmit Buffer Flush

1=SPITX cleared

0=SPITX not cleared

RXFLSH

Receive Buffer Flush

1=SPIRX cleared

0=SPIRX not cleared

25

ILPBK

Internal Loopback Enable

1=Internal loopback enabled

0=Internal loopback not enabled

Loading...

Loading...