ADSP-21368 SHARC Processor Hardware Reference A-55

Register Reference

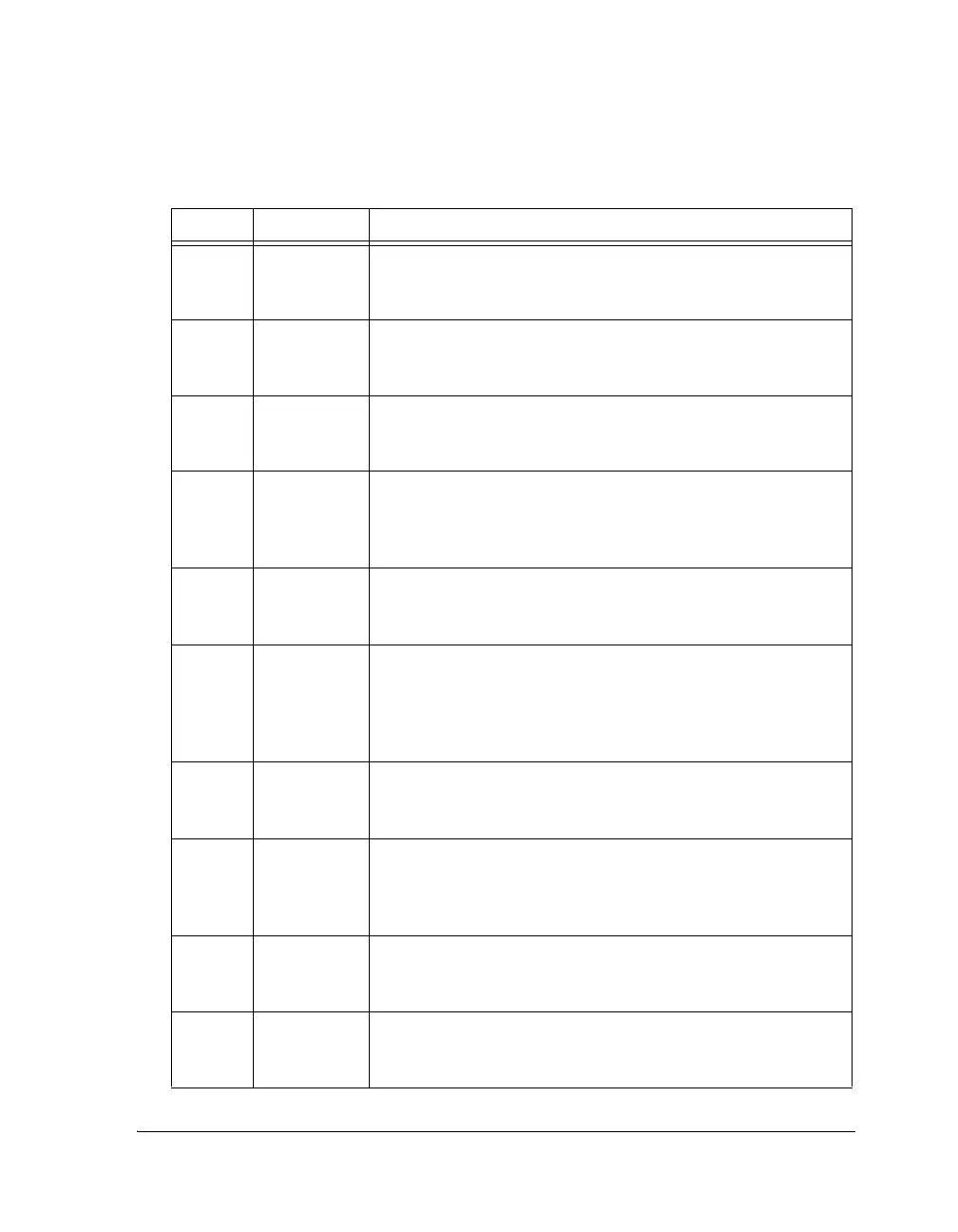

10 CPHASE Clock Phase. Selects the transfer format.

0 = SPICLK starts toggling at the middle of 1st data bit.

1 = SPICLK starts toggling at the start of 1st data bit.

11 CLKPL Clock Polarity.

0 = Active high SPICLK (SPICLK low is the idle state)

1 = Active low SPICLK (SPICLK high is the idle state)

12 SPIMS SPI Master Select. Configures SPI module as master or slave.

0 = Device is a slave device

1 = Device is a master device

13 OPD Open Drain Output Enable. Enables open drain data output

enable (for MOSI and MISO).

0 = Normal

1 = Open drain

14 SPIEN SPI Port Enable.

0 = SPI module is disabled

1 = SPI module is enabled

15 PACKEN Packing Enable.

0 = No packing

1 = 8- to16-bit packing

Note: This bit may be 1 only when WL = 00 (8-bit transfer). When

in transmit mode, the PACKEN bit unpacks data.

16 SGN Sign Extend.

0 = No sign extension

1 = Sign extension

17 SMLS Seamless Transfer.

0 = Seamless transfer disabled

1 = Seamless transfer enabled, not supported in mode

TIMOD1–0 = 00 and CPHASE=0 for all modes

18 TXFLSH Flush Transmit Buffer. Write a 1 to this bit to clear TXSPI.

0 = TXSPI not cleared

1 = TXSPI cleared

19 RXFLSH Clear RXSPI. Write a 1 to this bit to clear RXSPI.

0 = RXSPI not cleared

1 = RXSPI cleared

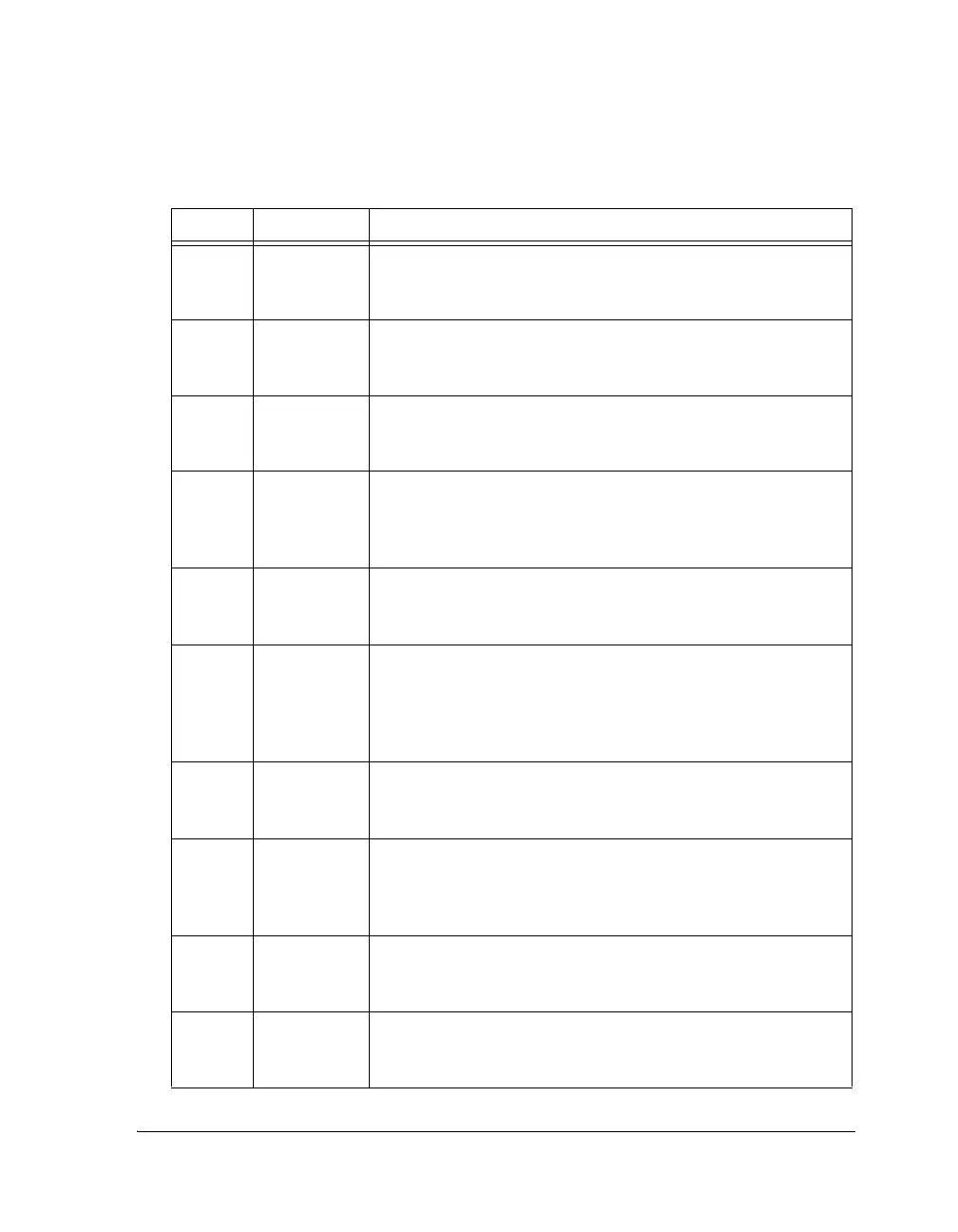

Table A-10. SPICTL Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...