Serial Peripheral Interface Registers

A-62 ADSP-21368 SHARC Processor Hardware Reference

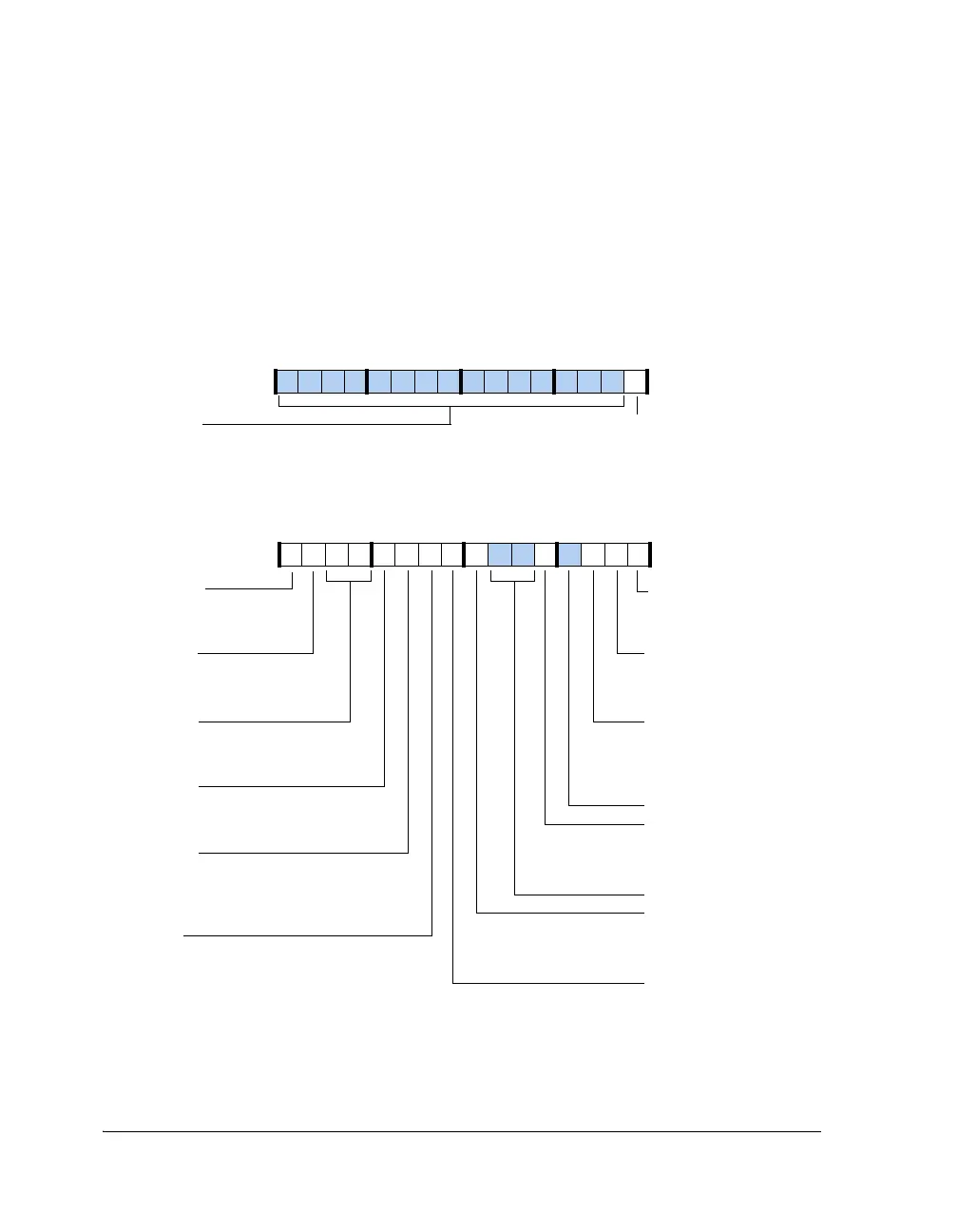

SPI DMA Configuration Registers (SPIDMAC, SPIDMACB)

These registers addresses are 0x1084 (for

SPIDMAC) and 0x2884 (for SPID-

MACB

) and their reset value is undefined. These 17-bit SPI registers, shown

in Figure A-26 and described in Table A-15, are used to control DMA

transfers.

Figure A-26. SPIDMAC, SPIDMACB Registers

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0000000000000000

SPICHS

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000000000000000

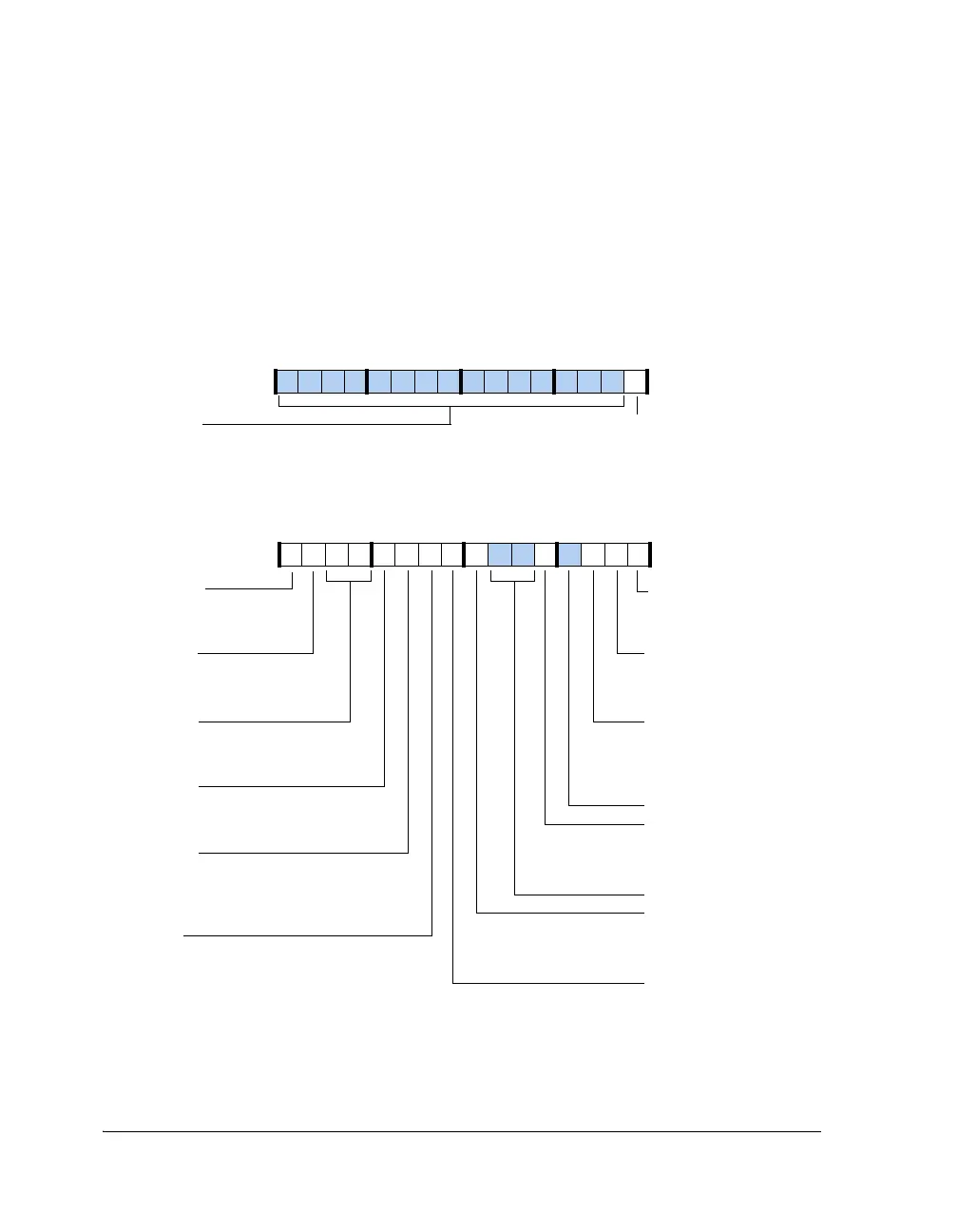

SPIDEN

SPIDMAS

DMA Transfer Status

1=DMA transfer in progress

0=DMA Idle

DMA Chain Loading Status

1=DMA chain pointer loading

in progress

0=DMA chain idle

SPIERRS

DMA Error Status

1=Error during transfer

0=Successful DMA transfer

SPISx

DMA FIFO Status

00=FIFO empty, 11=FIFO full,

10=FIFO partially full

DMA Enable

1=DMA enabled

0=DMA disabled

SPIRCV

DMA Write/Read

1=Memory read (SPI transmit)

0=Memory write (SPI receive)

SPIMME

Multimaster Error

1=Error during transfer

0=Successful transfer

SPIUNF

Transmit Underflow Error (SPIRCV=1)

1=Transmission error occurred with transmit

buffer empty

0=Successful transfer

Receive Overflow Error (SPIRCV=1)

1=Error: data received with receive buffer full

0=Successful transfer

SPIOVF

INTEN

Enable DMA Interrupt on

Transfer

1=Enable

0=Disable

Reserved

DMA FIFO Clear

1=Enable

0=Disable

FIFOFLSH

Enable Interrupt on Error

1=Enable

0=Disable

INTERR

SPI DMA Chaining Enable

1=Enable

0=Disable

SPICHEN

Reserved

SPIDMAC (0x1084)

SPIDMACB (0x2884)

Loading...

Loading...