ADSP-21368 SHARC Processor Hardware Reference A-63

Register Reference

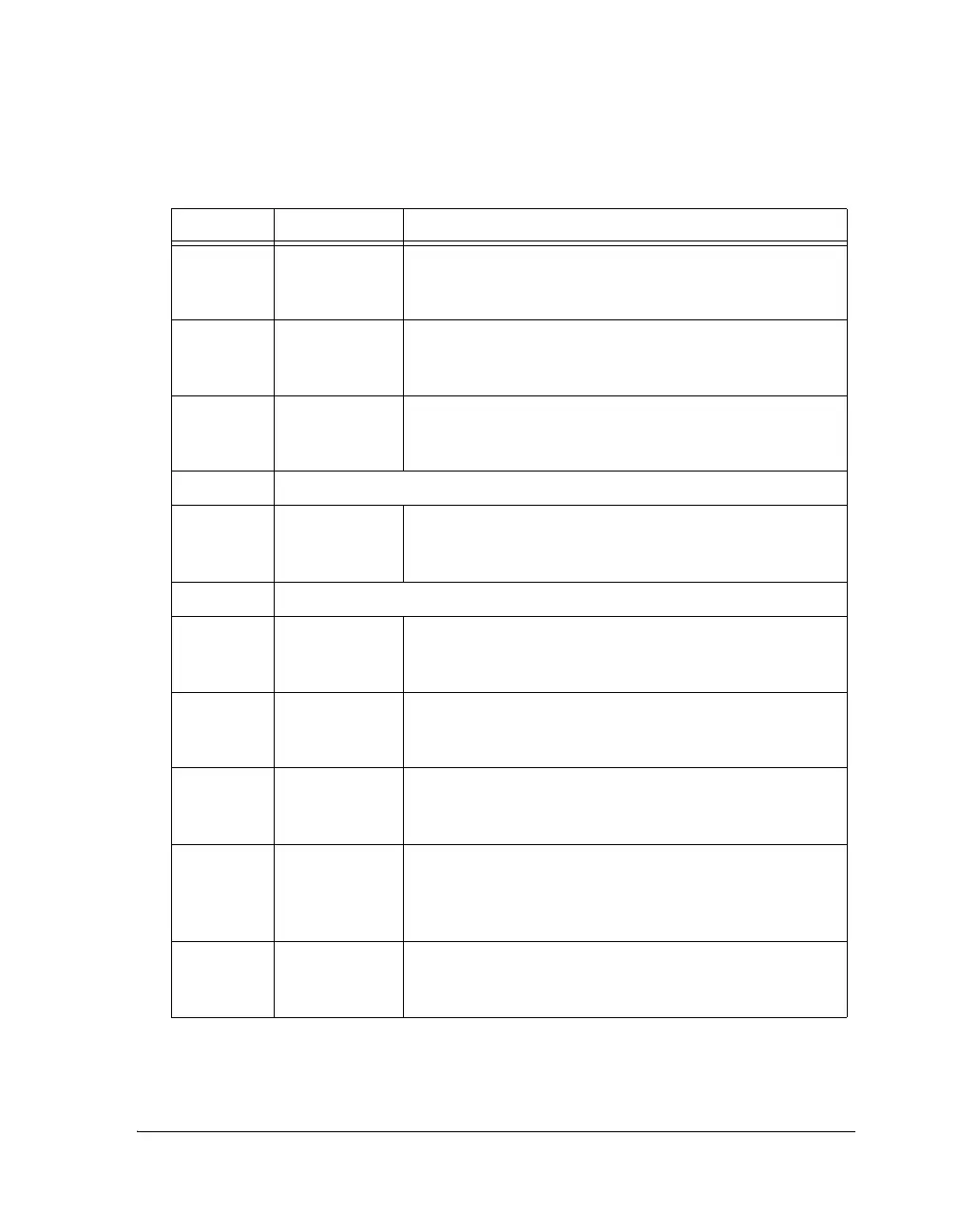

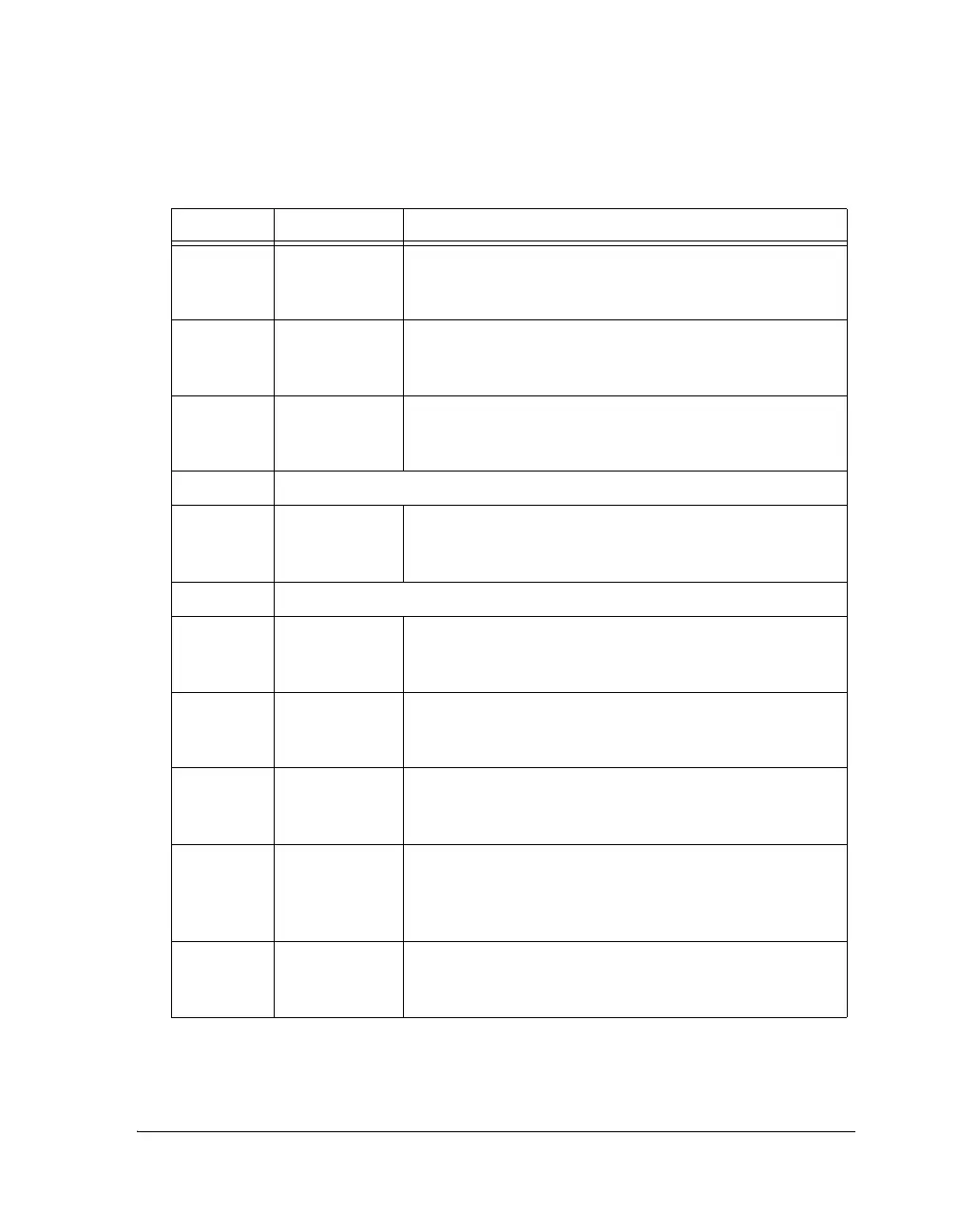

Table A-15. SPIDMAC, SPIDMACB Register Bit Descriptions

Bit Name Description

0SPIDENDMA Enable.

0 = Disable

1 = Enable

1SPIRCVDMA Write/Read.

0 = Memory write (SPI transmit)

1 = Memory read (SPI receive)

2INTENEnable DMA Interrupt on Transfer.

0 = Disable

1 = Enable

3Reserved

4SPICHENSPI DMA Chaining Enable.

0 = Disable

1 = Enable

6–5 Reserved

7FIFOFLSHDMA FIFO Clear.

0 = Disable

1 = Enable

8INTERREnable Interrupt on Error.

0 = Disable

1 = Enable

9SPIOVFReceive OverFlow Error (SPIRCV = 1).

0 = Successful transfer

1 = Error – data received with RXSPI full

10 SPIUNF Transmit Underflow Error (SPIRCV = 0).

0 = Successful transfer

1 = Error occurred in transmission with no new data in

TXSPI.

11 SPIMME Multimaster Error.

0 = Successful transfer

1 = Error during transfer

Loading...

Loading...