ADSP-21368 SHARC Processor Hardware Reference 2-21

I/O Processor

IOP channel arbitration can be set to use either a fixed or rotating algo-

rithm by setting or clearing bit 7 (

DCPR) in the SYSCTL register:

•fixed SYSCTL[7] cleared (0)

• rotating SYSCTL[7] set (1)

In the fixed priority scheme, the lower indexed peripheral has the highest

priority.

In the rotating priority scheme, the default priorities at reset are the same

as that of the fixed priority. However, the peripheral priority is deter-

mined by group, not individually. Peripheral groups are shown in

Table 2-5.

Initially, group A has the highest priority and group F the lowest. As one

group completes its DMA operation, it is assigned the lowest priority

(moves to the back of the line) and the next group is given the highest

priority.

When none of the peripherals request bus access, the highest priority

peripheral, for example, peripheral#0, is granted the bus. However, this

does not change the currently assigned priorities to various peripherals.

Within a peripheral group the priority is highest for the higher indexed

peripheral (see Table 2-5). For example, in SP01 (which is in group A),

SP1 has the highest priority.

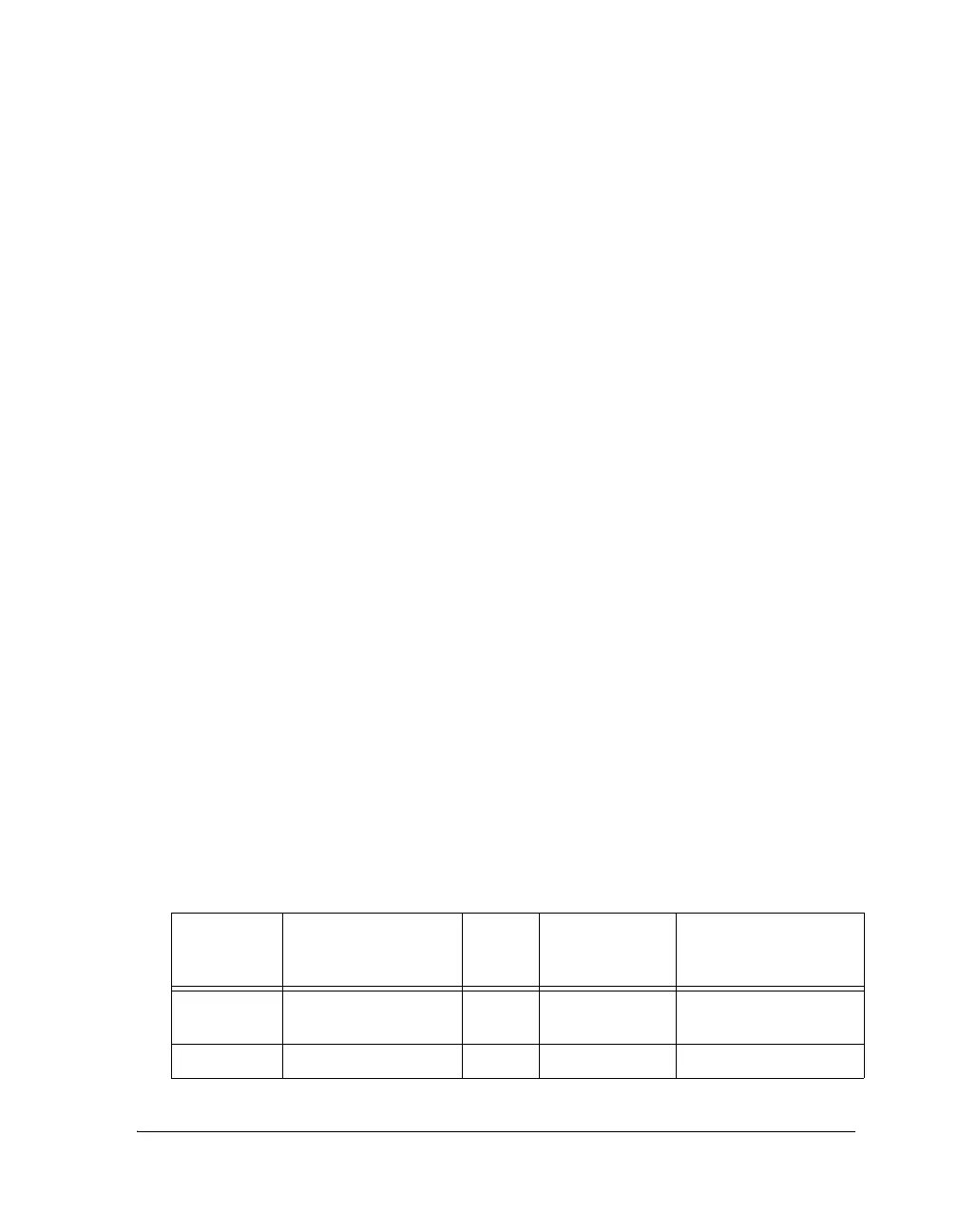

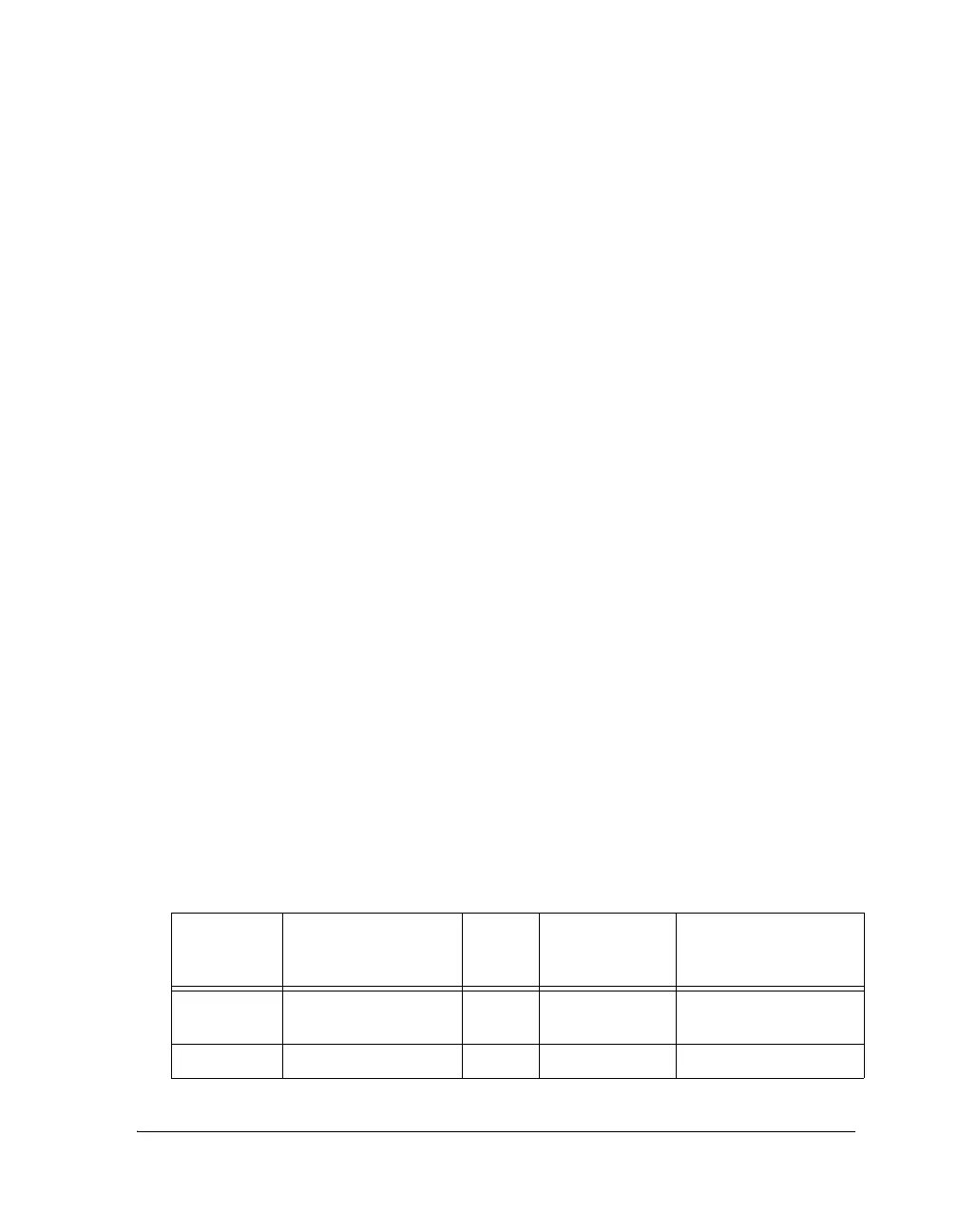

Table 2-5. DMA Channel Allocation and Parameter Register

Assignments

DMA

Channel

Number

Data Buffer Group IOP Address of

Data Buffers

Description

0 (highest

priority)

RXSP1A, TXSP1A A 0xC65, 0xC64 Serial Port 1A Data

1 RXSP1B, TXSP1B A 0xC67, 0xC66 Serial Port 1B Data

Loading...

Loading...