Configuring IOP/Core Interaction

2-22 ADSP-21368 SHARC Processor Hardware Reference

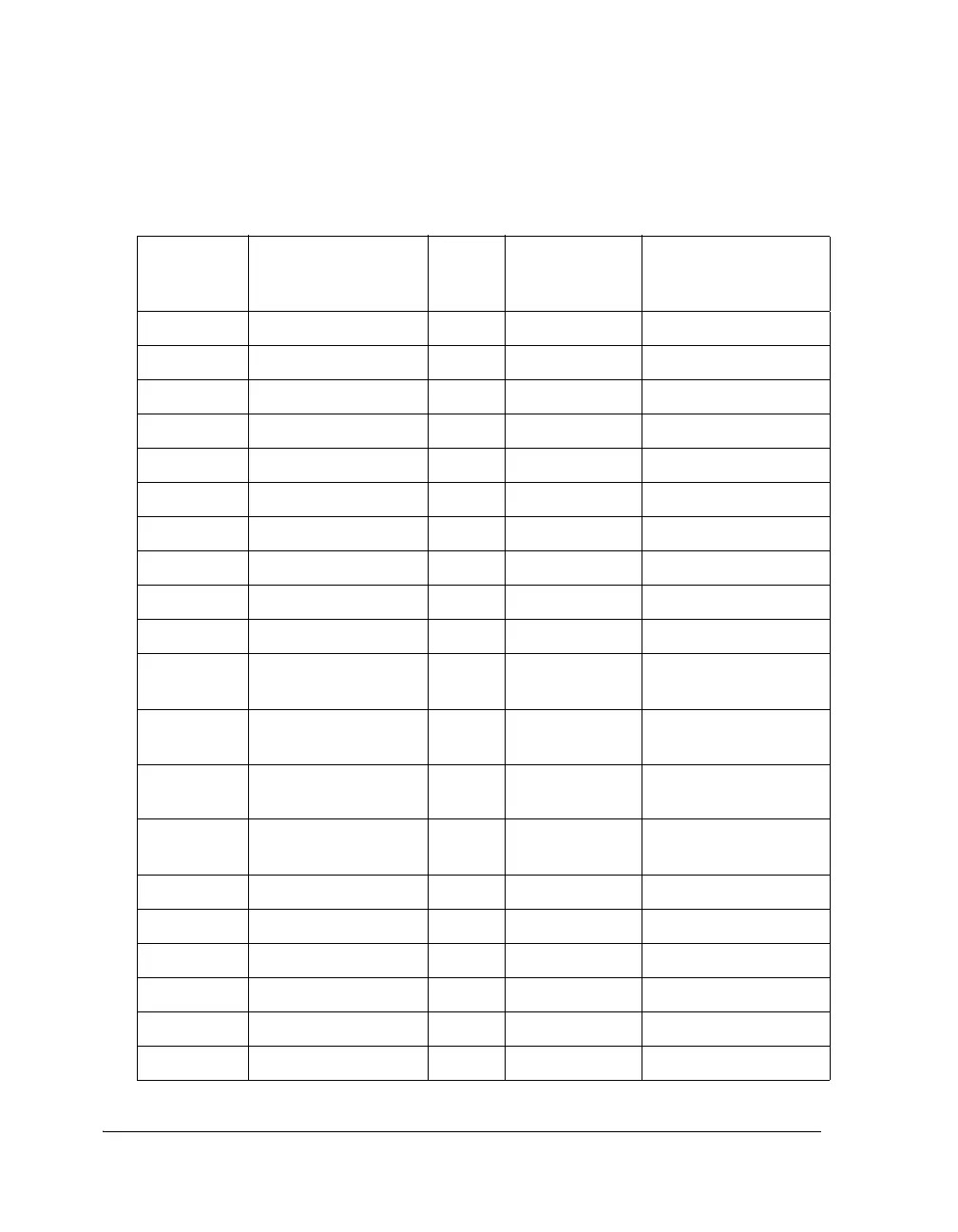

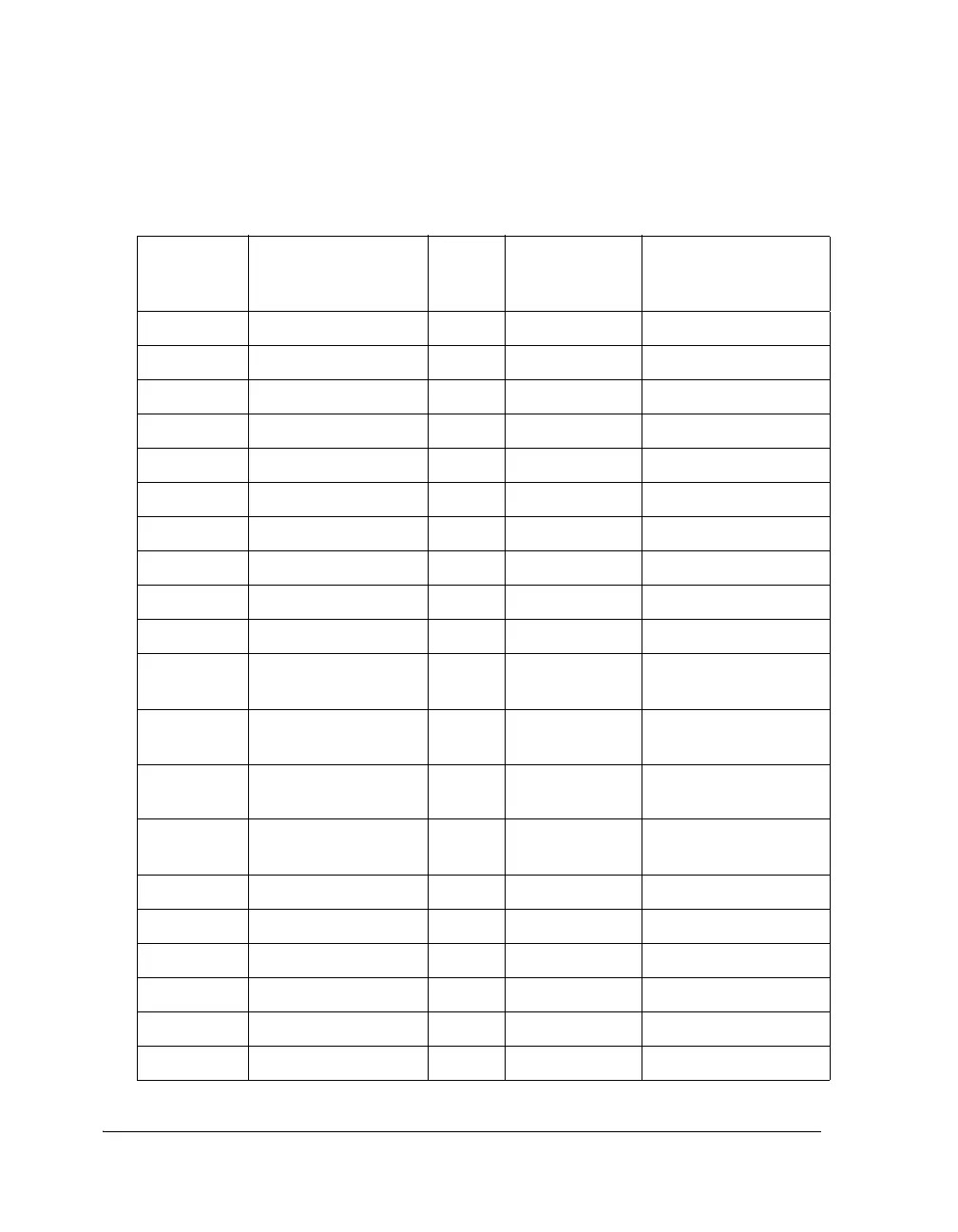

2 RXSP0A, TXSP0A A 0xC61, 0xC60 Serial Port 0A Data

3 RXSP0B, TXSP0B A 0xC63, 0xC62 Serial Port 0B Data

4 RXSP3A, TXSP3A B 0x465, 0x464 Serial Port 3A Data

5 RXSP3B, TXSP3B B 0x467, 0x466 Serial Port 3B Data

6 RXSP2A, TXSP2A B 0x461, 0x460 Serial Port 2A Data

7 RXSP2B, TXSP2B B 0x463, 0x462 Serial Port 2B Data

8 RXSP5A, TXSP5A C 0x865, 0x864 Serial Port 5A Data

9 RXSP5B, TXSP5B C 0x867, 0x866 Serial Port 5B Data

10 RXSP4A, TXSP4A C 0x861, 0x860 Serial Port 4A Data

11 RXSP4B, TXSP4B C 0x863, 0x862 Serial Port 4B Data

12 RXSP7A, TXSP7A C 0x04865,

0x04864

Serial Port 7A Data

13 RXSP7B, TXSP7B C 0x04867,

0x04866

Serial Port 7B Data

14 RXSP6A, TXSP6A C 0x04861 or

0x04860

Serial Port 6A Data

15 RXSP6B, TXSP6B C 0x04863 or

0x04862

Serial Port 6B Data

16 IDP_FIF0 D 0x24D0 DAI IDP Channel 0

17 IDP_FIF0 D 0x24D0 DAI IDP Channel 1

18 IDP_FIF0 D 0x24D0 DAI IDP Channel 2

19 IDP_FIF0 D 0x24D0 DAI IDP Channel 3

20 IDP_FIF0 D 0x24D0 DAI IPD Channel 4

21 IDP_FIF0 D 0x24D0 DAI IDP Channel 5

Table 2-5. DMA Channel Allocation and Parameter Register

Assignments (Cont’d)

DMA

Channel

Number

Data Buffer Group IOP Address of

Data Buffers

Description

Loading...

Loading...