ADSP-21368 SHARC Processor Hardware Reference 2-23

I/O Processor

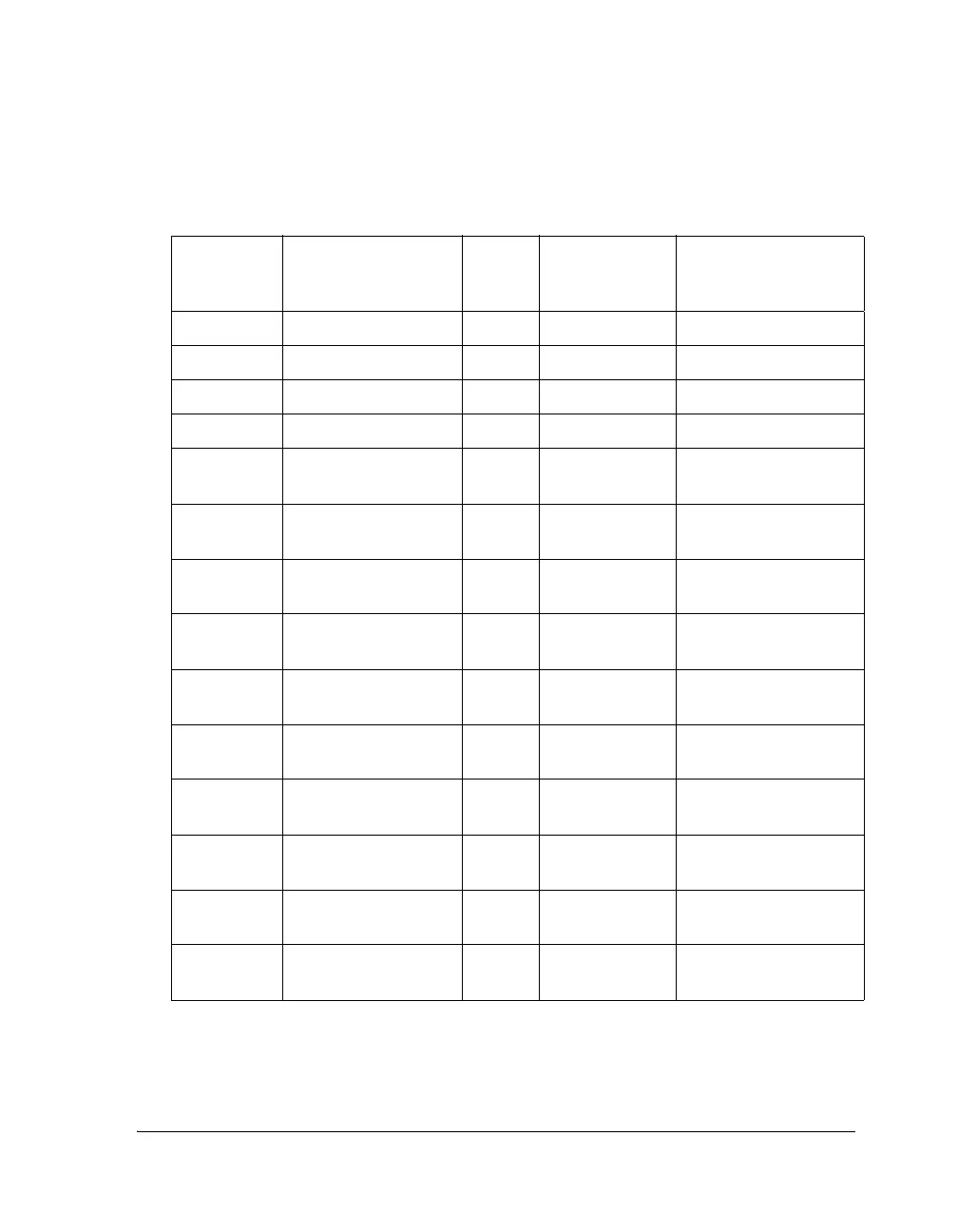

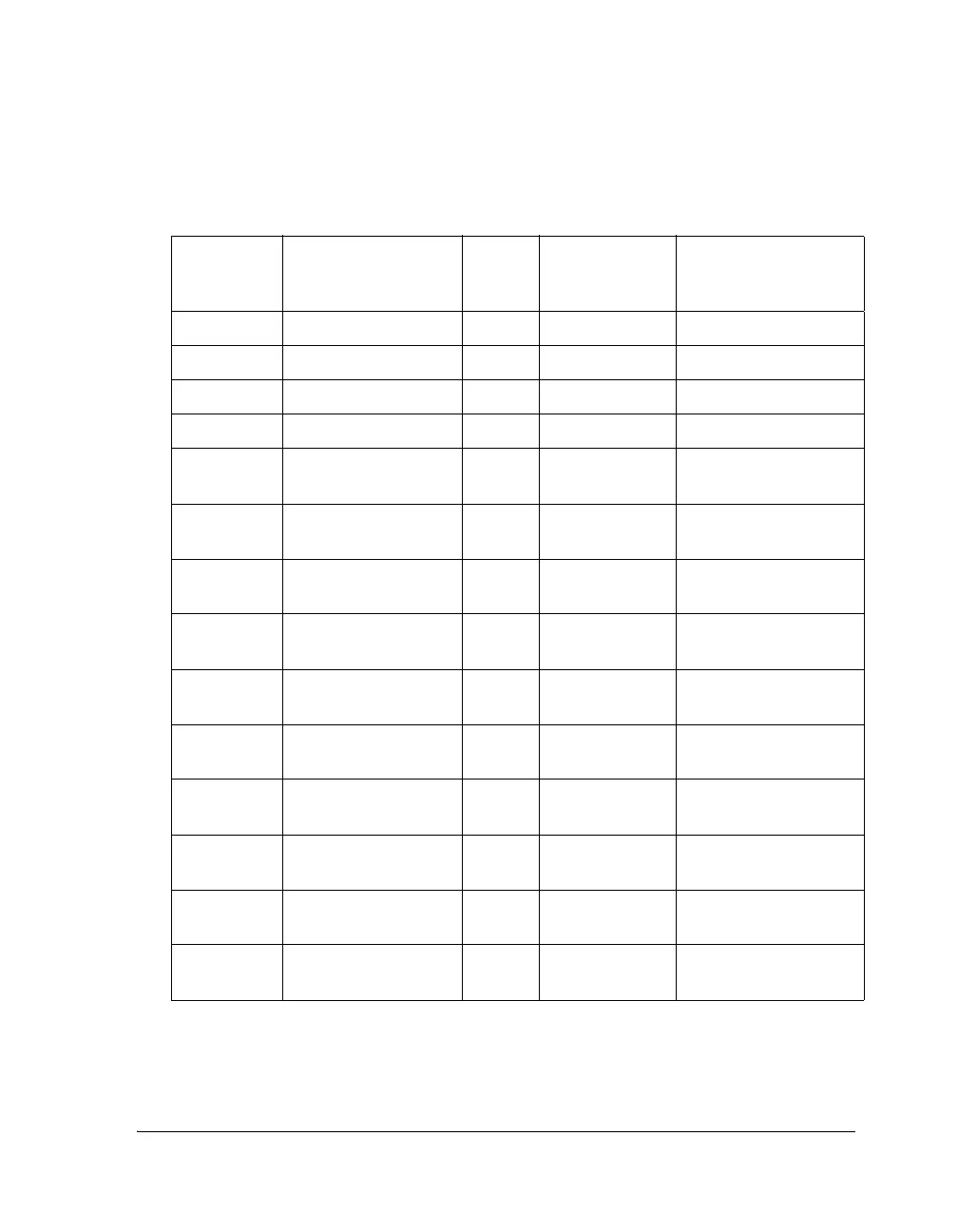

22 IDP_FIF0 D 0x24D0 DAI IDP Channel 6

23 IDP_FIF0 D 0x24D0 DAI IDP Channel 7

24 RXSPI, TXSPI E 0x1004, 0x1003 SPI Data

25 RXSPIB, TXSPIB G 0x2804, 0x2803 SPI Data

26 MTM Read FIFO G Not accessible Memory-to-Memory

Read Data

27 THR0 G 0x3C00 UART0 Transmit

Holding Register

28 RBR0 G 0x3C00 UART0 Receive Buffer

Register

29 THR1 G 0x4000 UART1 Transmit

Holding Register

30 RBR1 G 0x4000 UART1 Receive Buffer

Register

31 EPDF0 G 0x182C External Port Channel0

Data FIFO

32 EPTF0 G 0x182D External Port Channel0

Tap List FIFO

33 EPDF1 G 0x183C External Port Channel1

Data FIFO

34 EPTF1 G 0x183D External Port Channel1

Tap List FIFO

35 (lowest

priority)

MTM Write FIFO G Not accessible Memory-to Memory

Write Data

Table 2-5. DMA Channel Allocation and Parameter Register

Assignments (Cont’d)

DMA

Channel

Number

Data Buffer Group IOP Address of

Data Buffers

Description

Loading...

Loading...