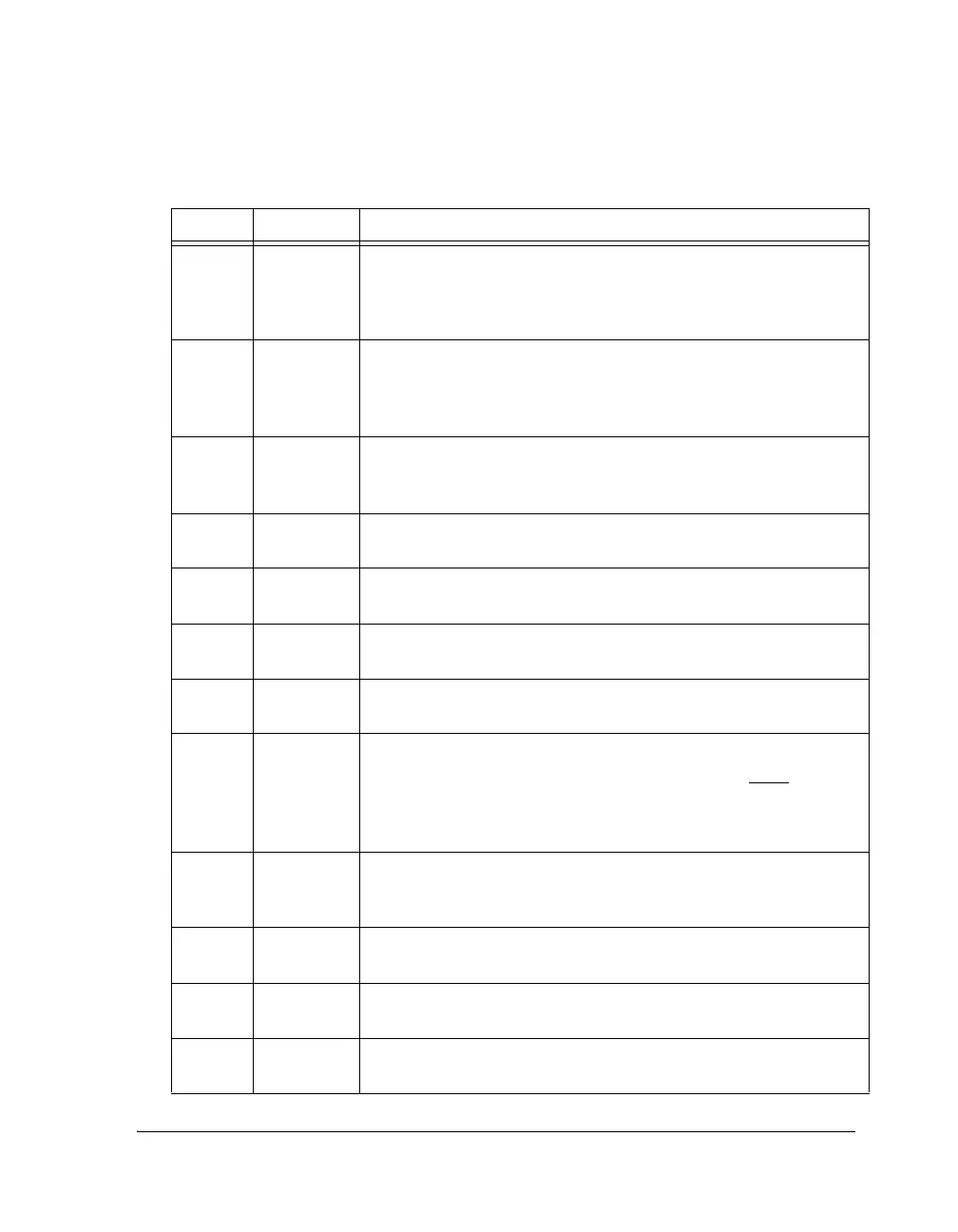

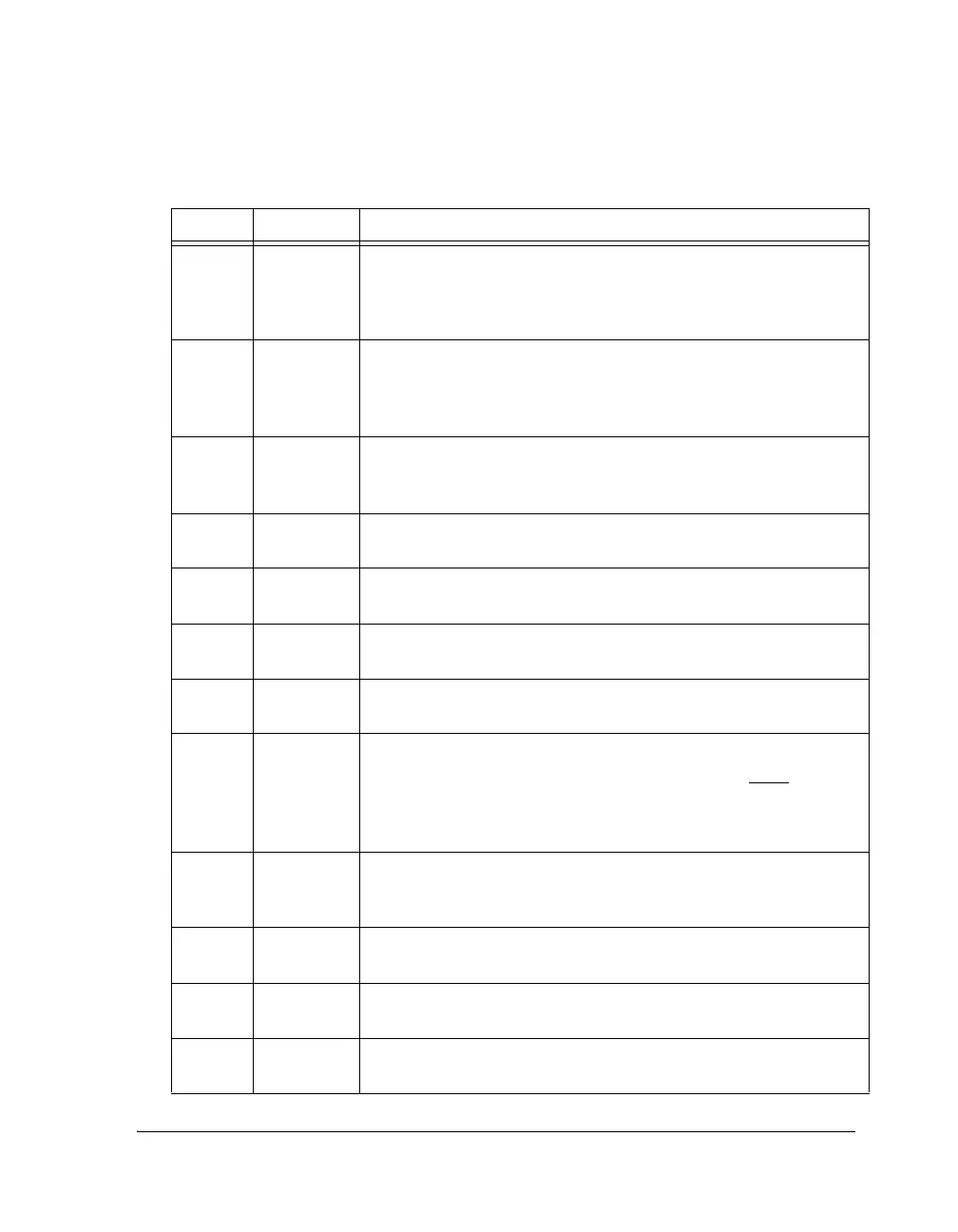

ADSP-21368 SHARC Processor Hardware Reference B-21

Interrupts

20 CB7I DAG1 Circular Buffer 7 Overflow Interrupt. Unmasks the CB7I inter-

rupt (if set, = 1), or masks the CB7I interrupt (if cleared, = 0). A circu-

lar buffer overflow occurs when the DAG circular buffering operation

increments the I register past the end of the buffer.

21 CB15I DAG2 Circular Buffer 15 Overflow Interrupt. Unmasks the CB15I

interrupt (if set, = 1), or masks the CB15I interrupt (if cleared, = 0). A

circular buffer overflow occurs when the DAG circular buffering opera-

tion increments the I register past the end of the buffer.

22 TMZLI Timer Expired (Low Priority) Interrupt. Unmasks the TMZLI inter-

rupt (if set, = 1), or masks the TMZLI interrupt (if cleared, = 0). For

more information, see “TMZHI” on page B-19.

23 FIXI Fixed-Point Overflow Interrupt. Unmasks the FIXI interrupt (if set, =

1), or masks the FIXI interrupt (if cleared, = 0).

24 FLTOI Floating-Point Overflow Interrupt. Unmasks the FLTOI interrupt (if

set, = 1), or masks the FLTOI interrupt (if cleared, = 0).

25 FLTUI Floating-Point Underflow Interrupt. Unmasks the FLTUI interrupt (if

set, = 1), or masks the FLTUI interrupt (if cleared, = 0).

26 FLTII Floating-Point Invalid Operation Interrupt. Unmasks the FLTII inter-

rupt (if set, = 1), or masks the FLTII interrupt (if cleared, = 0).

27 EMULI Emulator (Lower Priority) Interrupt. Unmasks the EMULI interrupt

(if set, = 1), or masks the EMULI interrupt (if cleared, = 0). An EMULI

occurs on reset and when an external device asserts the EMU

pin.

This interrupt has a lower priority than EMUI, but higher

priority than software interrupts.

28 SFT0I User Software Interrupt 0. Unmasks the SFT0I interrupt (if set, = 1),

or masks the SFT0I interrupt (if cleared, = 0). An SFT0I occurs when a

program sets (= 1) this bit.

29 SFT1I User Software Interrupt 1. Unmasks the SFT1I interrupt (if set, = 1),

or masks the SFT1I interrupt (if cleared, = 0).

30 SFT2I User Software Interrupt 2. Unmasks the SFT2I interrupt (if set, = 1),

or masks the SFT2I interrupt (if cleared, = 0).

31 SFT3I User Software Interrupt 3. Unmasks the SFT3I interrupt (if set, = 1),

or masks the SFT3I interrupt (if cleared, = 0).

Table B-6. IMASK Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...