Setting Up DMA Parameter Registers

2-32 ADSP-21368 SHARC Processor Hardware Reference

In the serial port pair SP0/1, SP1 has a higher priority. For multichannel

pairs, the odd numbered channels have a higher priority (for example SP3,

SP5).

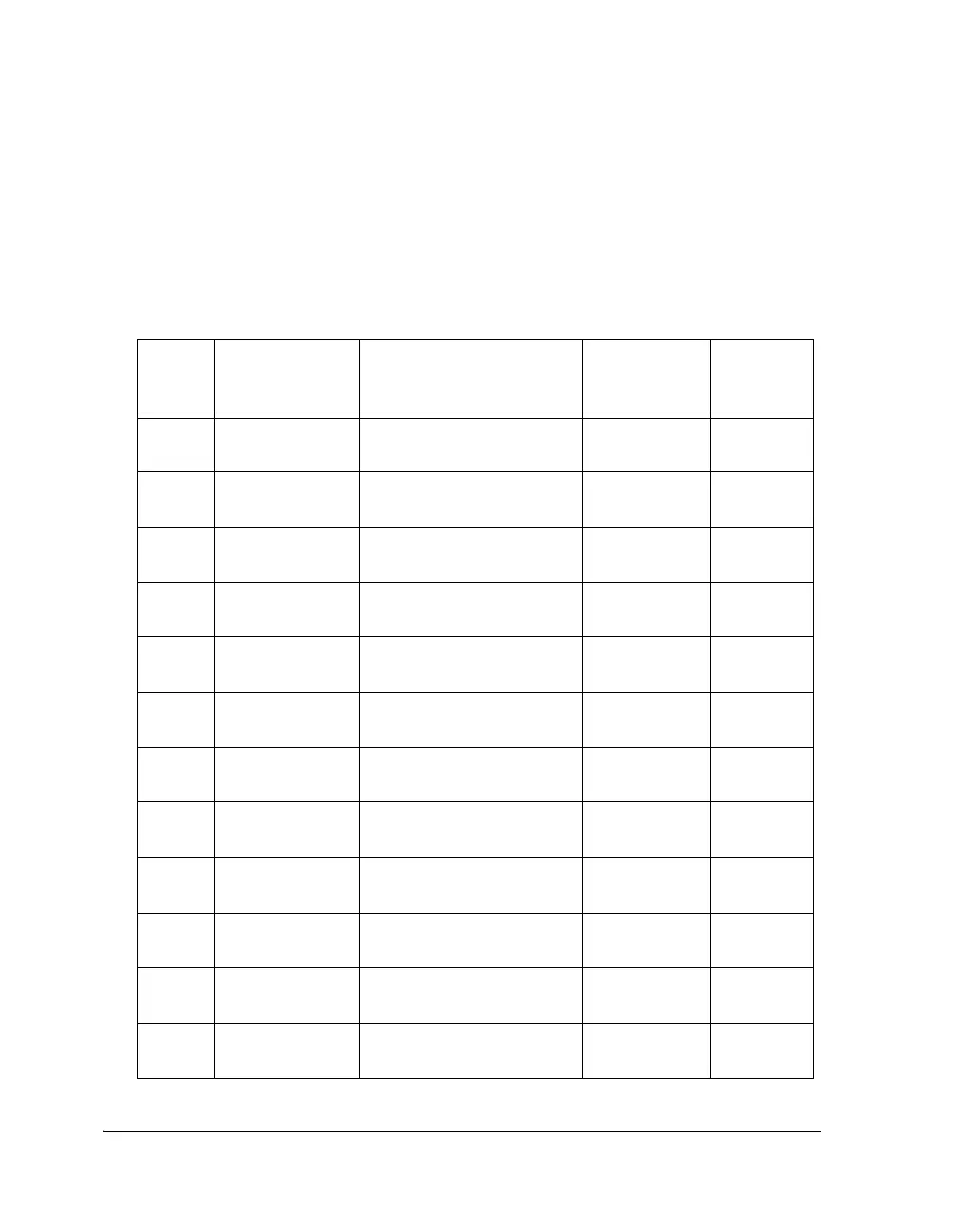

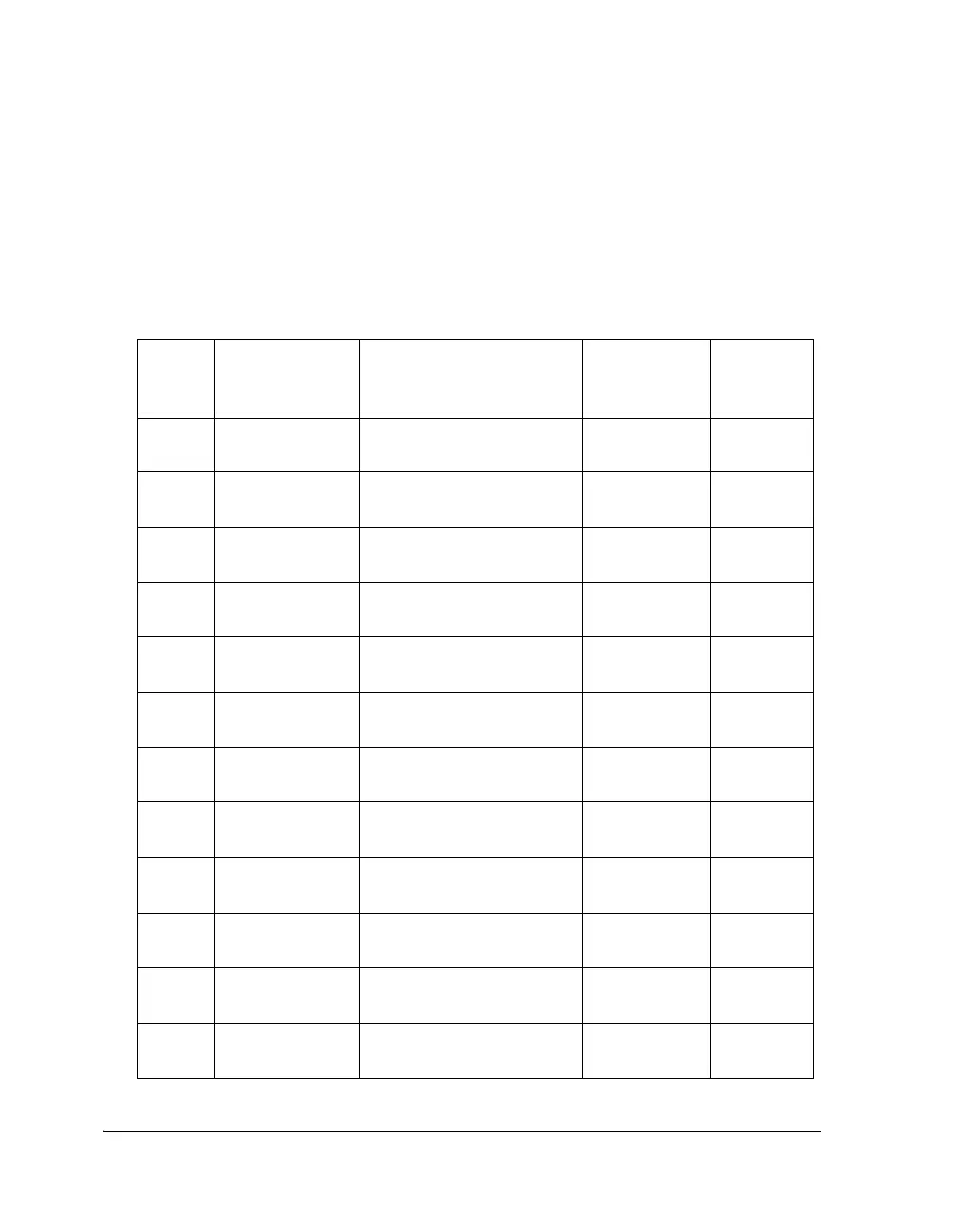

Table 2-7. DMA Channel Registers: Controls, Parameters,

and Buffers

DMA

Channel

Number

Control Registers Parameter Registers Buffer Registers Description

0 SPCTL1 IISP1A, IMSP1A, CSP1A,

CPSP1A

RXSP1A,

TXSP1A

Serial Port

1A Data

1 SPCTL1 IISP1B, IMSP1B, CSP1B,

CPSP1B

RXSP1B,

TXSP1B

Serial Port

1B Data

2 SPCTL0 IISP0A, IMSP0A, CSP0A,

CPSP0A

RXSP0A,

TXSP0A

Serial Port

0A Data

3 SPCTL0 IISP0B, IMSP0B, CSP0B,

CPSP0B

RXSP0B,

TXSP0B

Serial Port

0B Data

4 SPCTL3 IISP3A, IMSP3A, CSP3A,

CPSP3A

RXSP3A,

TXSP3A

Serial Port

3A Data

5 SPCTL3 IISP3B, IMSP3B, CSP3B,

CPSP3B

RXSP3B,

TXSP3B

Serial Port

3B Data

6 SPCTL2 IISP2A, IMSP2A, CSP2A,

CPSP2A

RXSP2A,

TXSP2A

Serial Port

2A Data

7 SPCTL2 IISP2B, IMSP2B, CSP2B,

CPSP2B

RXSP2B,

TXSP2B

Serial Port

2B Data

8 SPCTL5 IISP5A, IMSP5A, CSP5A,

CPSP5A

RXSP5A,

TXSP5A

Serial Port

5A Data

9 SPCTL5 IISP5B, IMSP5B, CSP5B,

CPSP5B

RXSP5B,

TXSP5B

Serial Port

5B Data

10 SPCTL4 IISP4A, IMSP4A, CSP4A,

CPSP4A

RXSP4A,

TXSP4A

Serial Port

4A Data

11 SPCTL4 IISP4B, IMSP4B, CSP4B,

CPSP4B

RXSP4B,

TXSP4B

Serial Port

4B Data

Loading...

Loading...