ADSP-21368 SHARC Processor Hardware Reference 2-33

I/O Processor

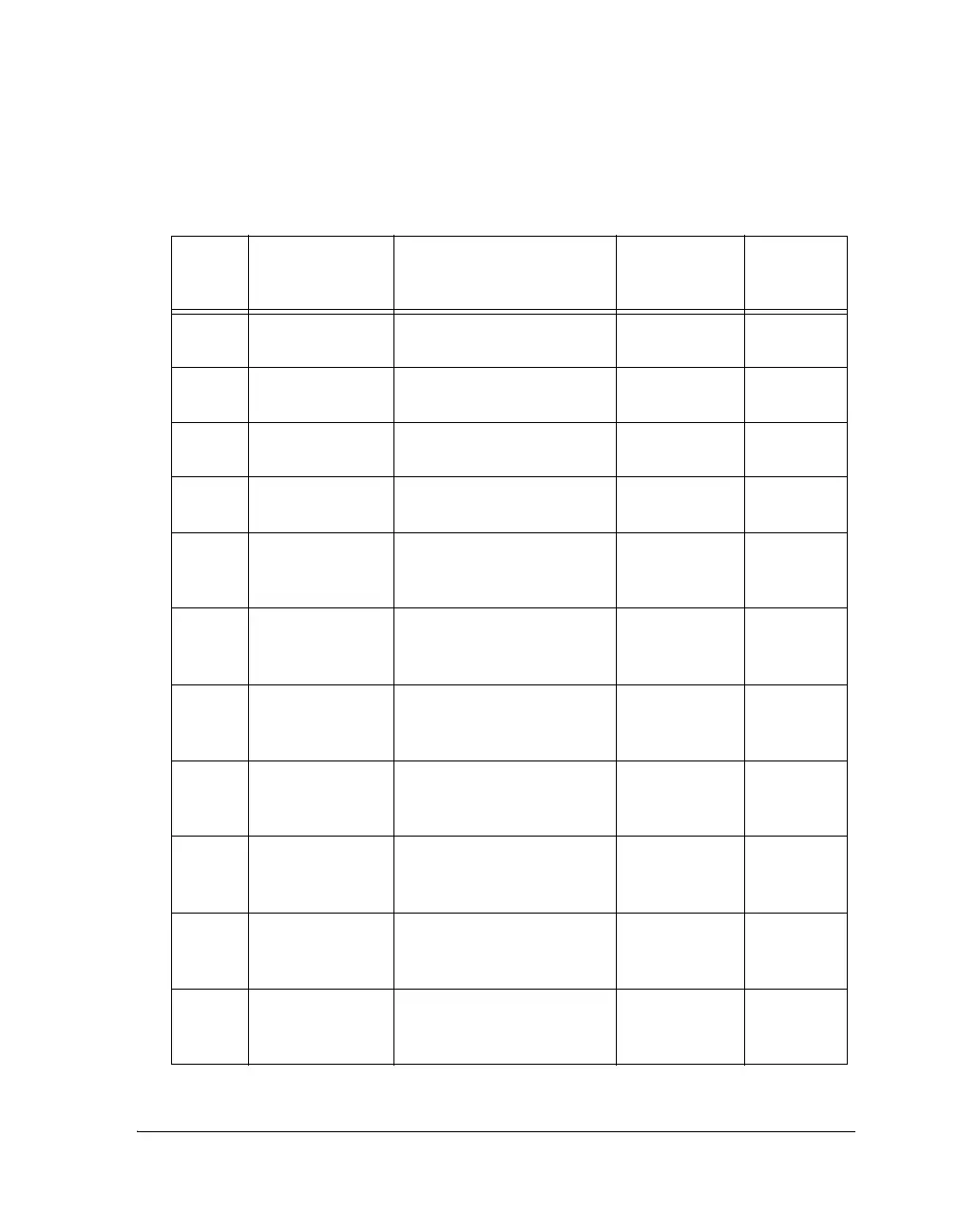

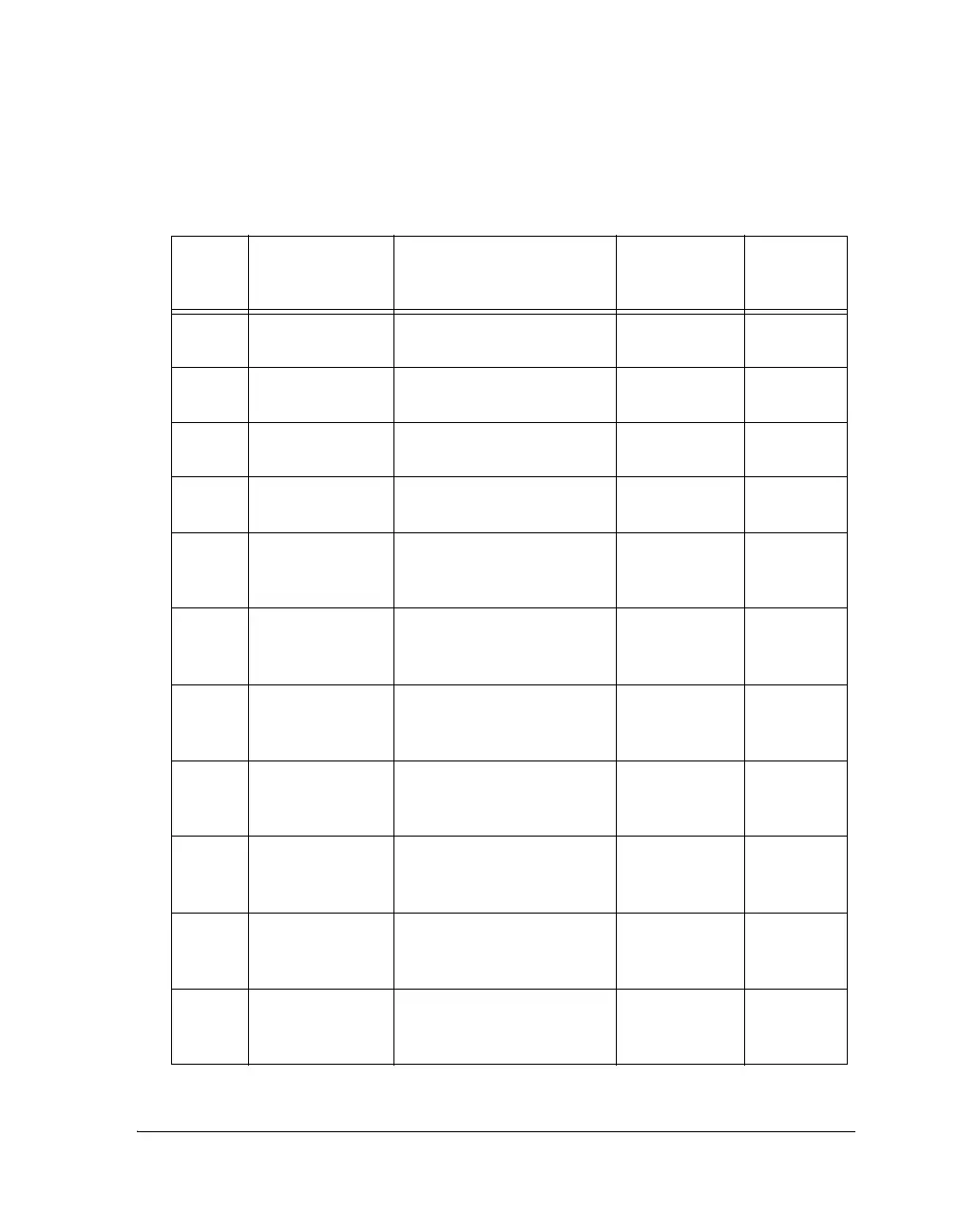

12 SPCTL7 IISP7A, IM7P5A, CSP7A,

CPSP7A

RXSP7A,

TXSP7A

Serial Port

7A Data

13 SPCTL7 IISP7B, IMSP7B, CSP7B,

CPSP7B

RXSP7B,

TXSP7B

Serial Port

7B Data

14 SPCTL6 IISP6A, IMSP6A, CSP6A,

CPSP6A

RXSP6A,

TXSP6A

Serial Port

6A Data

15 SPCTL6 IISP6B, IMSP6B, CSP6B,

CPSP6B

RXSP6B,

TXSP6B

Serial Port

6B Data

16 IDP_CTL IDP_DMA_I0,

IDP_DMA_M0,

IDP_DMA_C0

IDP_FIFO DAI IDP

Channel 0

17 IDP_CTL IDP_DMA_I1,

IDP_DMA_M1,

IDP_DMA_C1

IDP_FIFO DAI IDP

Channel 1

18 IDP_CTL IDP_DMA_I2,

IDP_DMA_M2,

IDP_DMA_C2

IDP_FIFO DAI IDP

Channel 2

19 IDP_CTL IDP_DMA_I3,

IDP_DMA_M3,

IDP_DMA_C3

IDP_FIFO DAI IDP

Channel 3

20 IDP_CTL IDP_DMA_I4,

IDP_DMA_M4,

IDP_DMA_C4

IDP_FIFO DAI IDP

Channel 4

21 IDP_CTL IDP_DMA_I5,

IDP_DMA_M5,

IDP_DMA_C5

IDP_FIFO DAI IDP

Channel 5

22 IDP_CTL IDP_DMA_I6,

IDP_DMA_M6,

IDP_DMA_C6

IDP_FIFO DAI IDP

Channel 6

Table 2-7. DMA Channel Registers: Controls, Parameters,

and Buffers (Cont’d)

DMA

Channel

Number

Control Registers Parameter Registers Buffer Registers Description

Loading...

Loading...