ADSP-21368 SHARC Processor Hardware Reference 3-55

External Port

Even if the external data width is 16 bits, the ADSP-21367/8/9 and

ADSP-2137x SHARC processors support only 32-bit data accesses. If

X16DE is enabled (=1) the SDC performs two 16-bit accesses to get and

place 32-bit data. The SDC takes the IA address and appends one extra bit

to the LSB to generate the address externally.

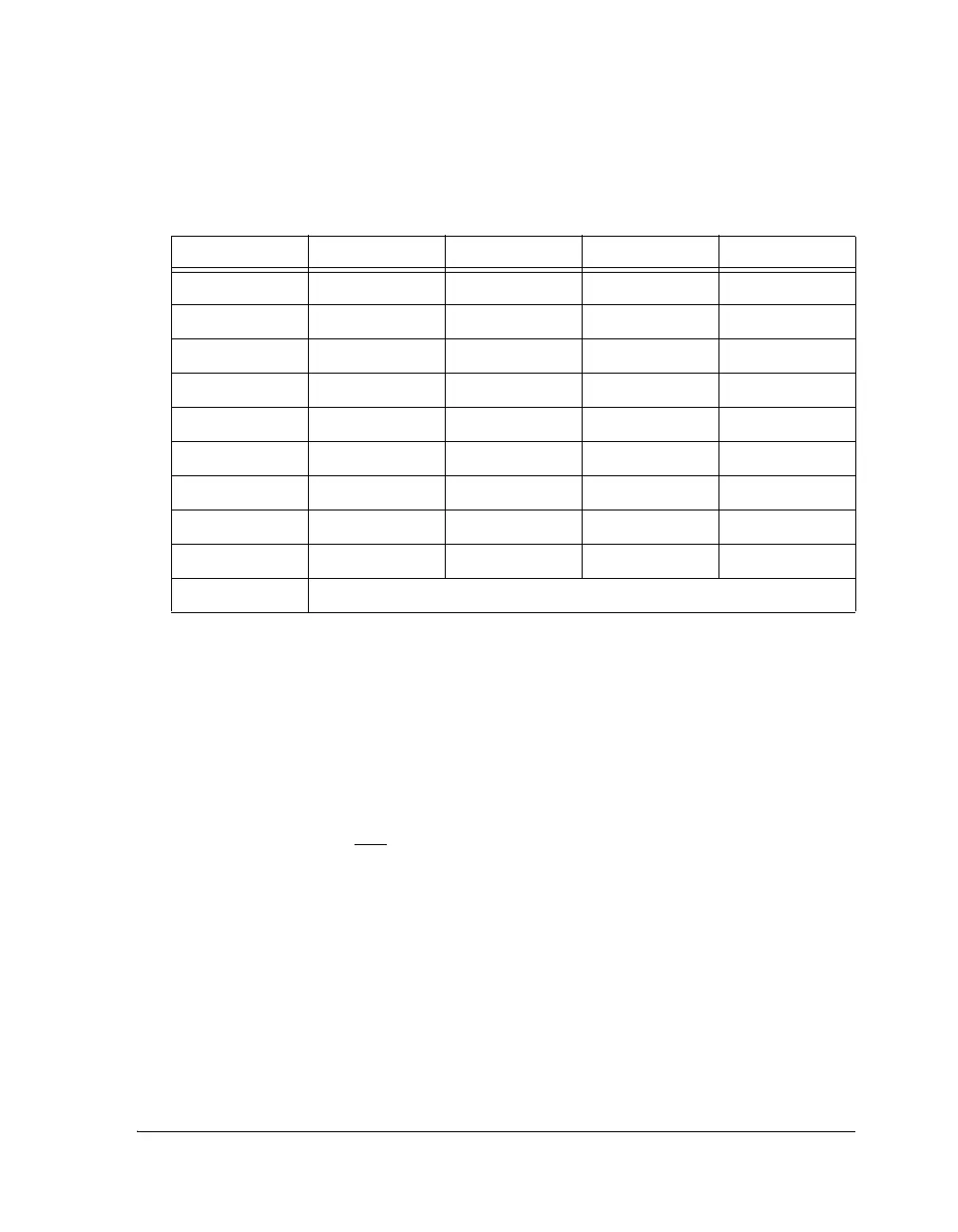

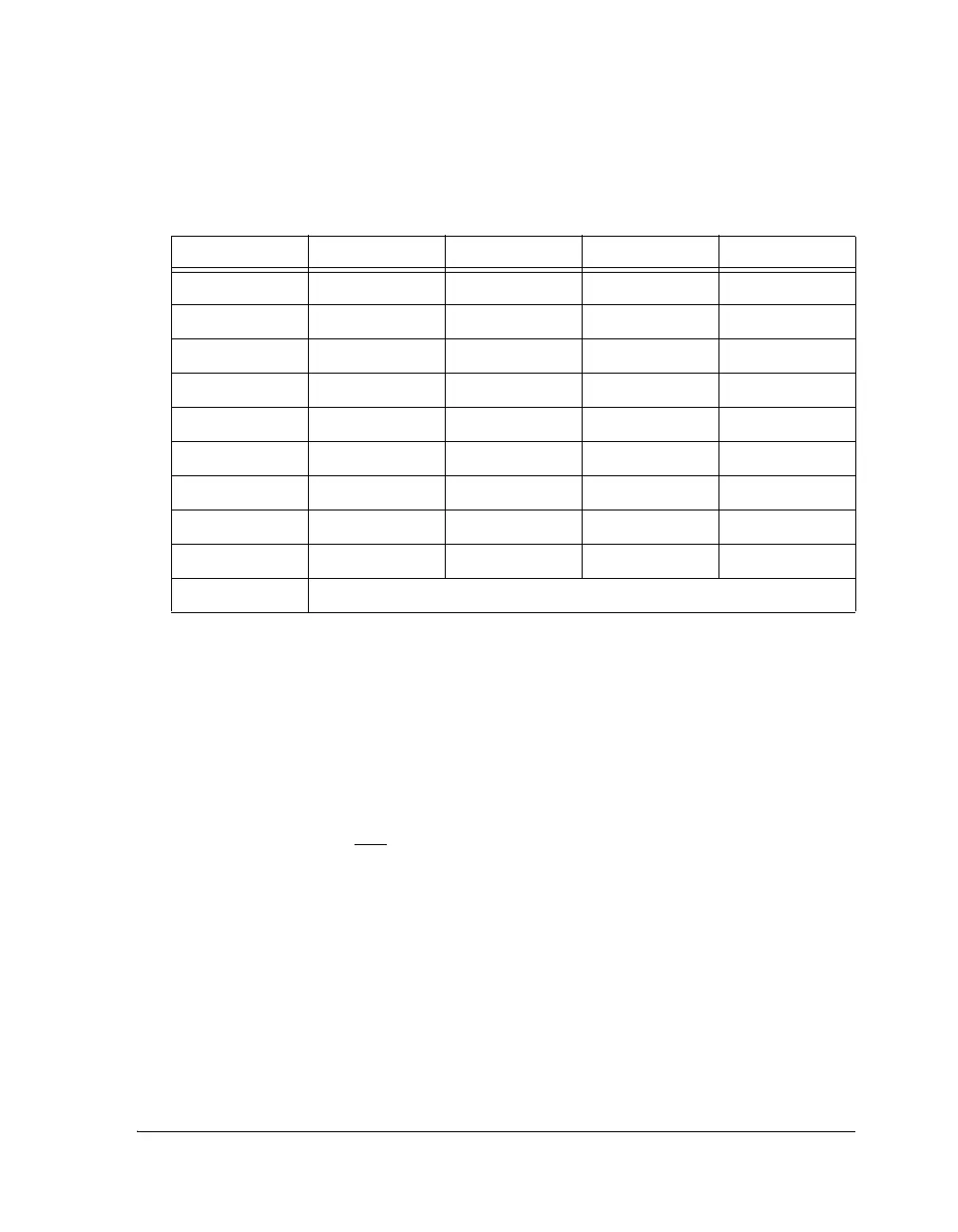

For example, if the processor core requests address 0x200–0000 for a

32-bit access, the SDC performs two 16-bit accesses at 0x000–0000 and

0x000–0001, using

MS0 to get one 32-bit data word. The column and row

addresses seen by 16-bit SDRAMs is shown in Table 3-24 where

X16DE = 1, SDRAW[2:0] = 100 (12 bits), and SDCAW[1:0] = 10 (10 bits) and

Table 3-25 where

X16DE = 1, SDRAW[2:0] = 100 (12 bits), and

SDCAW[1:0] = 11 (11 bits).

A[9] IA[8] IA[19] A[8]

A[8] IA[7] IA[18] A[7]

A[7] IA[6] IA[17] A[6]

A[6] IA[5] IA[16] A[5]

A[5] IA[4] IA[15] A[4]

A[4] IA[3] IA[14] A[3]

A[3] IA[2] IA[13] A[2]

A[2] IA[1] IA[12] A[1]

A[1] IA[0] IA[11] A[0]

A[0] Not USED for 32-bit SDRAMs

Table 3-23. 32-Bit Column, Row and Bank Address Mapping

(2K Words) (Cont’d)

Pin Column Address Row Address Bank Address Pins of SDRAM

Loading...

Loading...