SDRAM Controller

3-72 ADSP-21368 SHARC Processor Hardware Reference

commands with no effect, the

NOP command is given. When the SDC is

not accessing any SDRAM external banks, the command inhibit com-

mand is given.

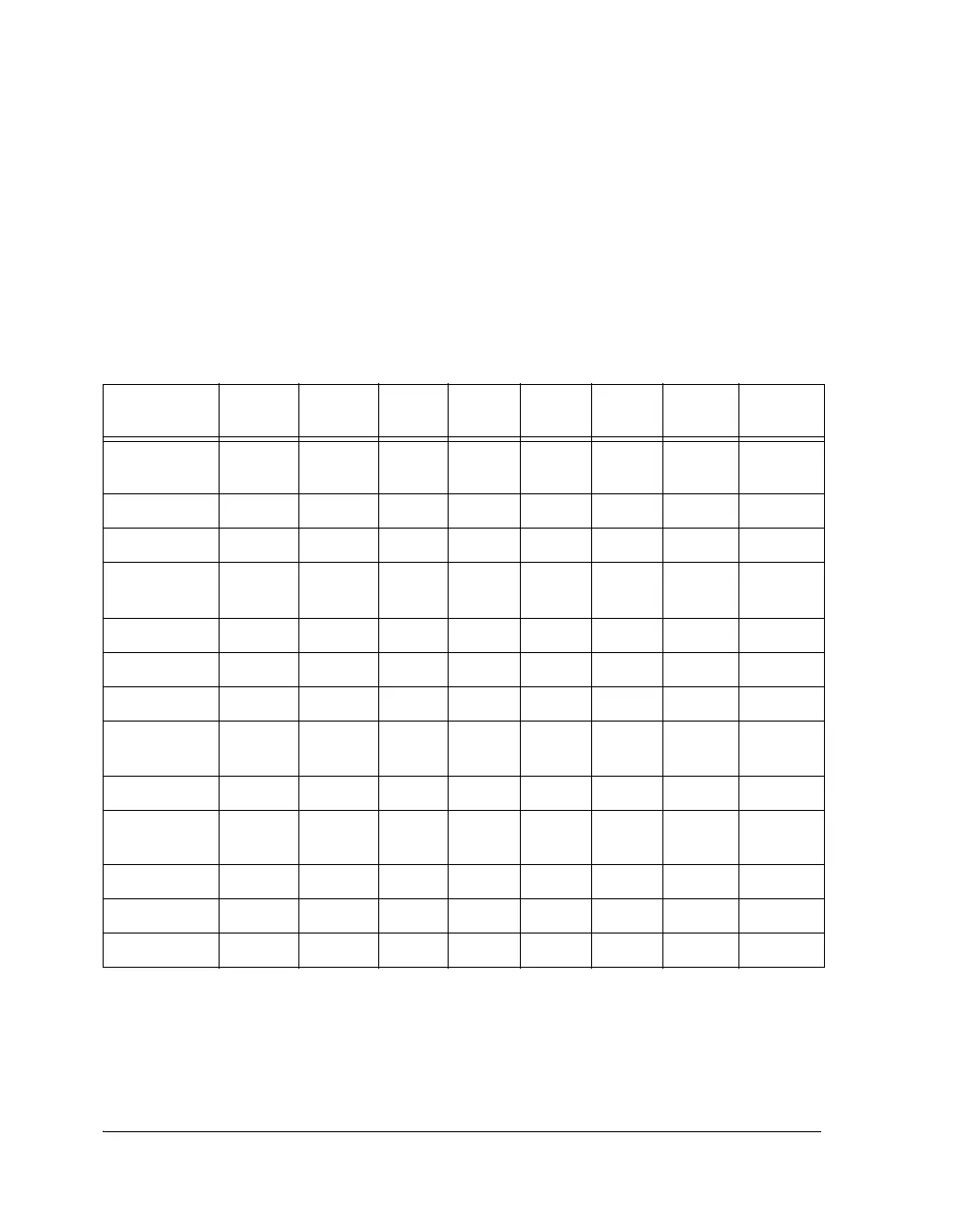

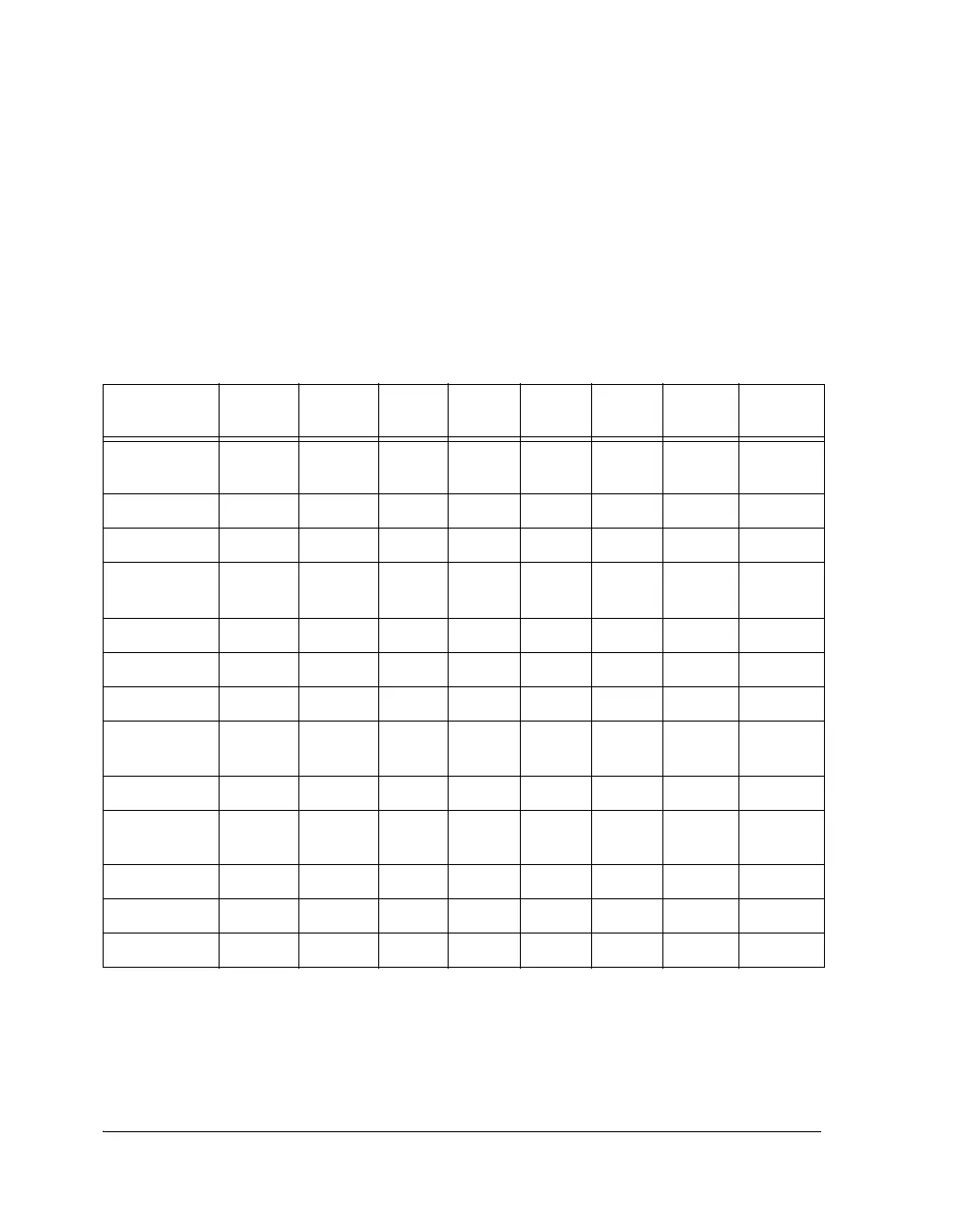

A summary of pin states during SDC commands appears in Table 3-26.

Note that an X means do not care.

Table 3-26. SDRAM Pin States During SDC Commands

Command SDCKE

(n-1)

SDCKE

(n)

MS3–0 SDRAS SDCAS SDWE SDA10 Addresses

Mode register

set

High High Low Low Low Low Opcode Opcode

Activate High High Low Low High Low Valid Valid

Read High High Low High Low High Low Valid

Single

Precharge

High High Low Low High Low Low Valid

Precharge all High High Low Low High Low High X

Write High High Low High Low Low Low Valid

Auto-refresh High High Low Low Low High X X

Self-refresh

entry

High Low Low Low Low High X X

Self-refreshLowLowXXXXX X

Self-refresh

exit

LowHighHighXXXX X

Burst Stop High High Low High High Low X X

Nop High High Low High High High X X

Inhibit High High High X X X X X

Loading...

Loading...