Making Connections in the SRUs

4-26 ADSP-21368 SHARC Processor Hardware Reference

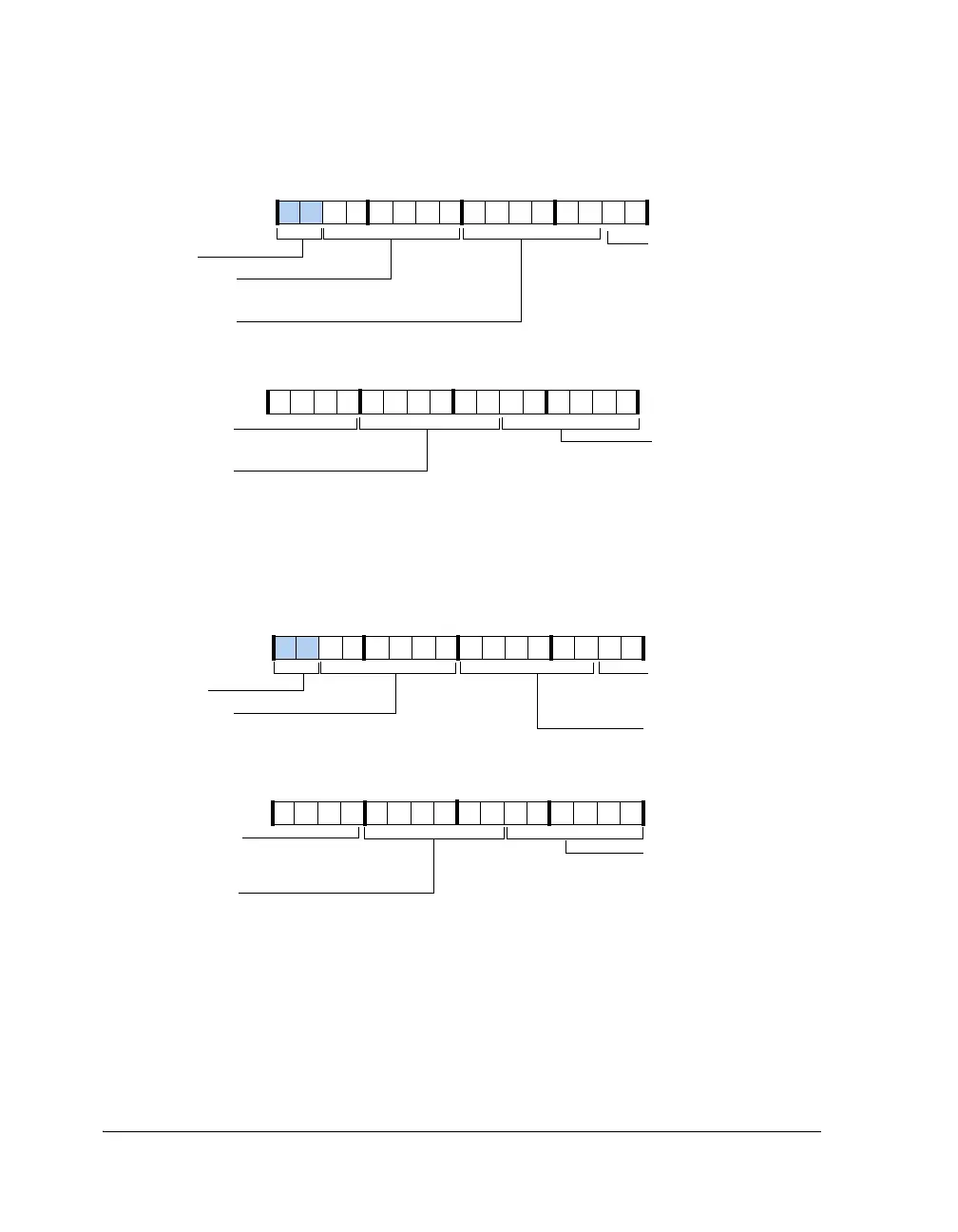

Figure 4-19. SRU_DAT1 Register

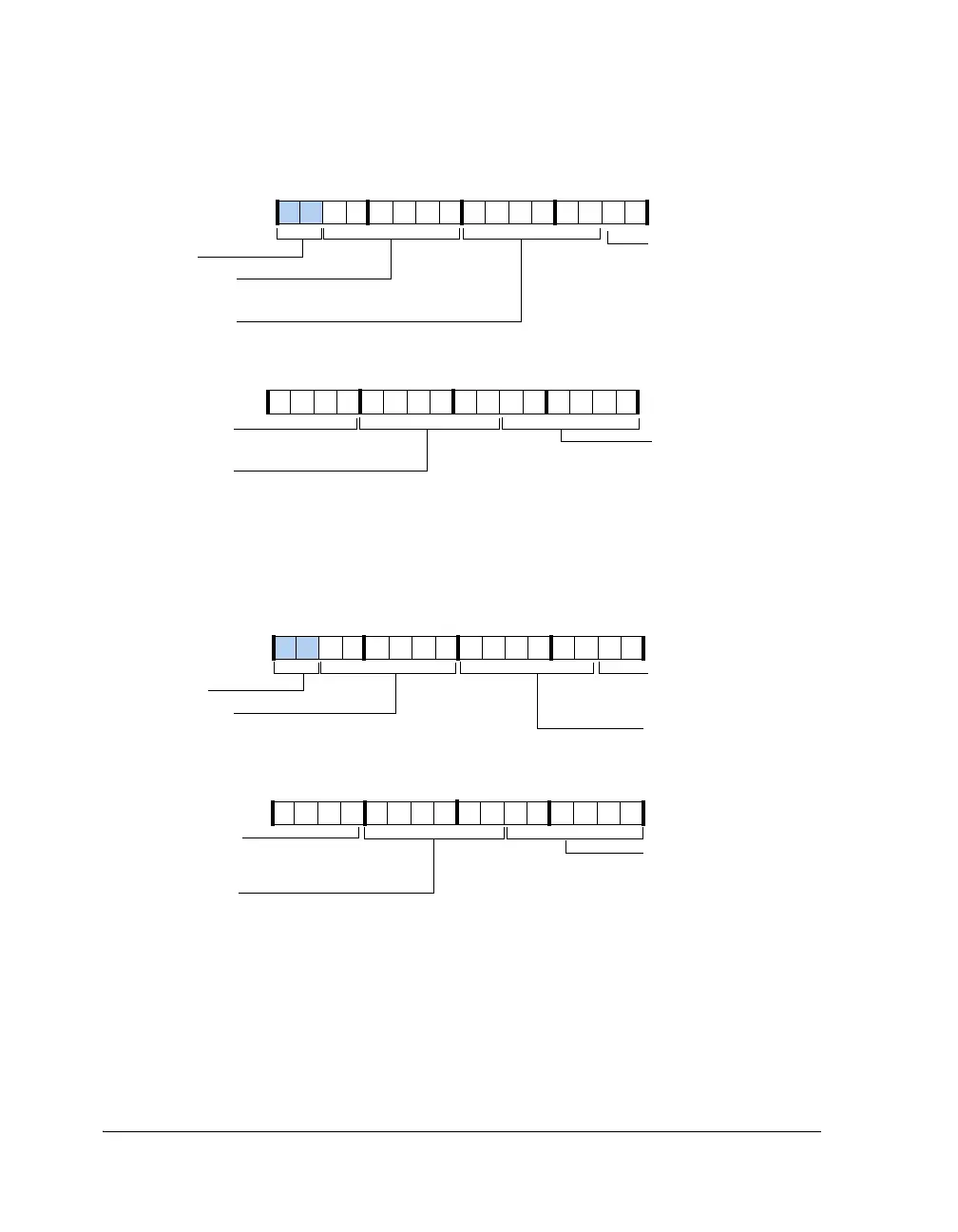

Figure 4-20. SRU_DAT2 Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0000011110011100

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

1101100101000100

Serial Port 4 Data Channel B Input

SPORT4_DB_I

Serial Port 3 Data

Channel B Input

SPORT3_DB_I

Serial Port 4 Data Channel A Input

SPORT4_DA_I

Serial Port 3 Data Channel A Input

SPORT3_DA_I

Serial Port 2 Data

Channel B Input

SPORT2_DB_I

SRU_DAT1 (0x2441)

SPORT3_DB_I

Reset = 0x0F38B289

Serial Port 3 Data Channel B Input

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000001000101000

Serial Port 5 Data Channel B Input

SPORT5_DB_I

Serial Port 5 Data

Channel A Input

SPORT5_DA_I

SRU_DAT2 (0x2442)

SRC0_DAT_IP_I

Reset = 0x00000450

Sample Rate Converter 2

Data Input Input

SRC2_DAT_IP_I

Sample Rate Converter 1

Data Input Input

SRC1_DAT_IP_I

Sample Rate Converter 0

Data Input Input

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0000000000000000

SRC0_DAT_IP_I

Sample Rate Converter 0

Data Input Input

Loading...

Loading...