Making Connections in the SRUs

4-44 ADSP-21368 SHARC Processor Hardware Reference

L

The following notes apply to group E connections.

1. SRU_EXT_MISCB is a 30-bit register. On reads, bits 30 and 31

always return zero.

2. A detailed description of the DAI interrupt register and its

usage is provided in “DAI Interrupt Controller Registers”

on page A-112.

3. Setting SRU_MISCA[30] to high inverts the level of MISCA4_I,

and setting SRU_MISCA[31] to high inverts the level of

MISCA5_I.

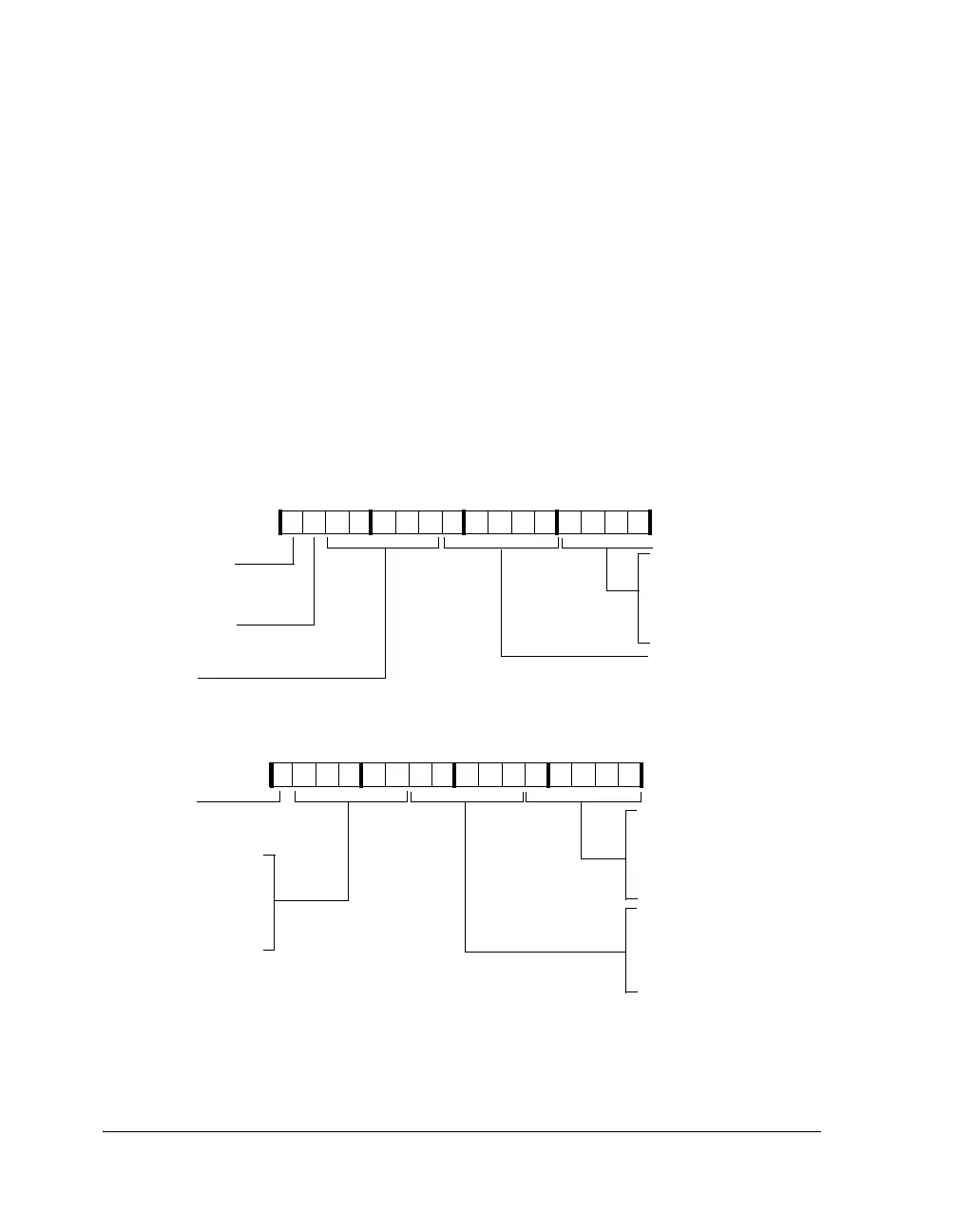

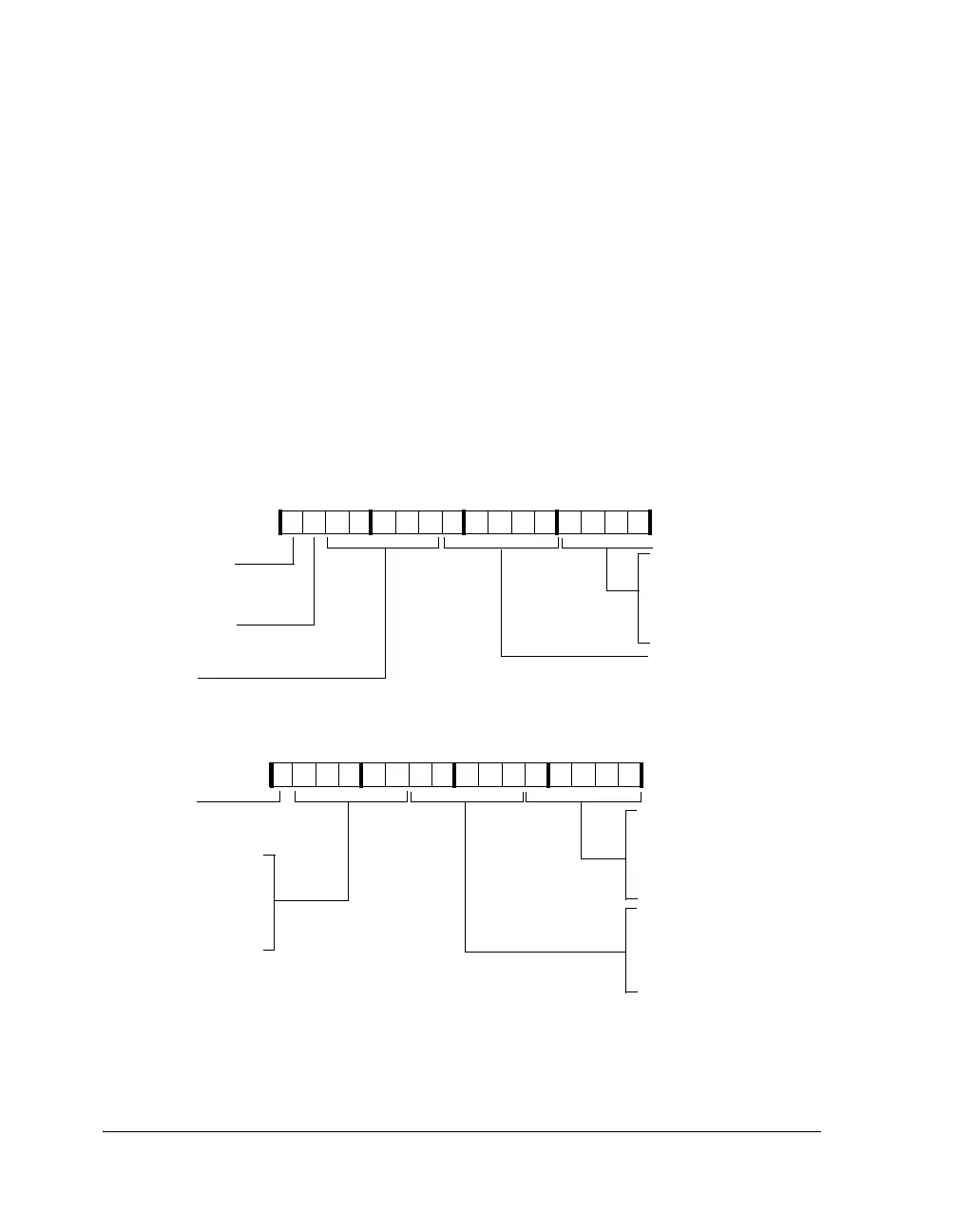

Figure 4-35. SRU_MISCA Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

1001111011110111

MISCA5_INVERT

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0011110111101111

Invert Miscellaneous

Channel A 4

MISCA4_INVERT

External Miscellaneous

Channel A 3

MISCA3_I

Invert Miscellaneous

Channel A 5

External Miscellaneous

Channel A 5

MISCA5_I

External Miscellaneous

Channel A 3

MISCA4_I

External Miscellaneous

Channel A 2

MISCA2_I

External Miscellaneous

Channel A 0

MISCA0_I

External Miscellaneous

Channel A 1

MISCA1_I

DAI Interrupt 31

DAI_INT_31

DAI Interrupt 30

DAI_INT_30

DAI Interrupt 28

DAI_INT_28

DAI Interrupt 29

DAI_INT_29

SRU_MISCA (0x2470)

MISCA3_I

External Miscellaneous

Channel A 3

Reset = 0x3DEF7BDE

Loading...

Loading...