Serial Port Signals

5-8 ADSP-21368 SHARC Processor Hardware Reference

If the SPORT is configured as a serial receiver (

SPTRAN = 0), the receive

portion of the SPORT shifts in data from the

SPORTx_DA or SPORTx_DB sig-

nal, synchronous to the SPORTx_CLK receive clock. If framing signals are

used, the

SPORTx_FS signal indicates the beginning of the serial word being

received. When an entire word is shifted in on the primary

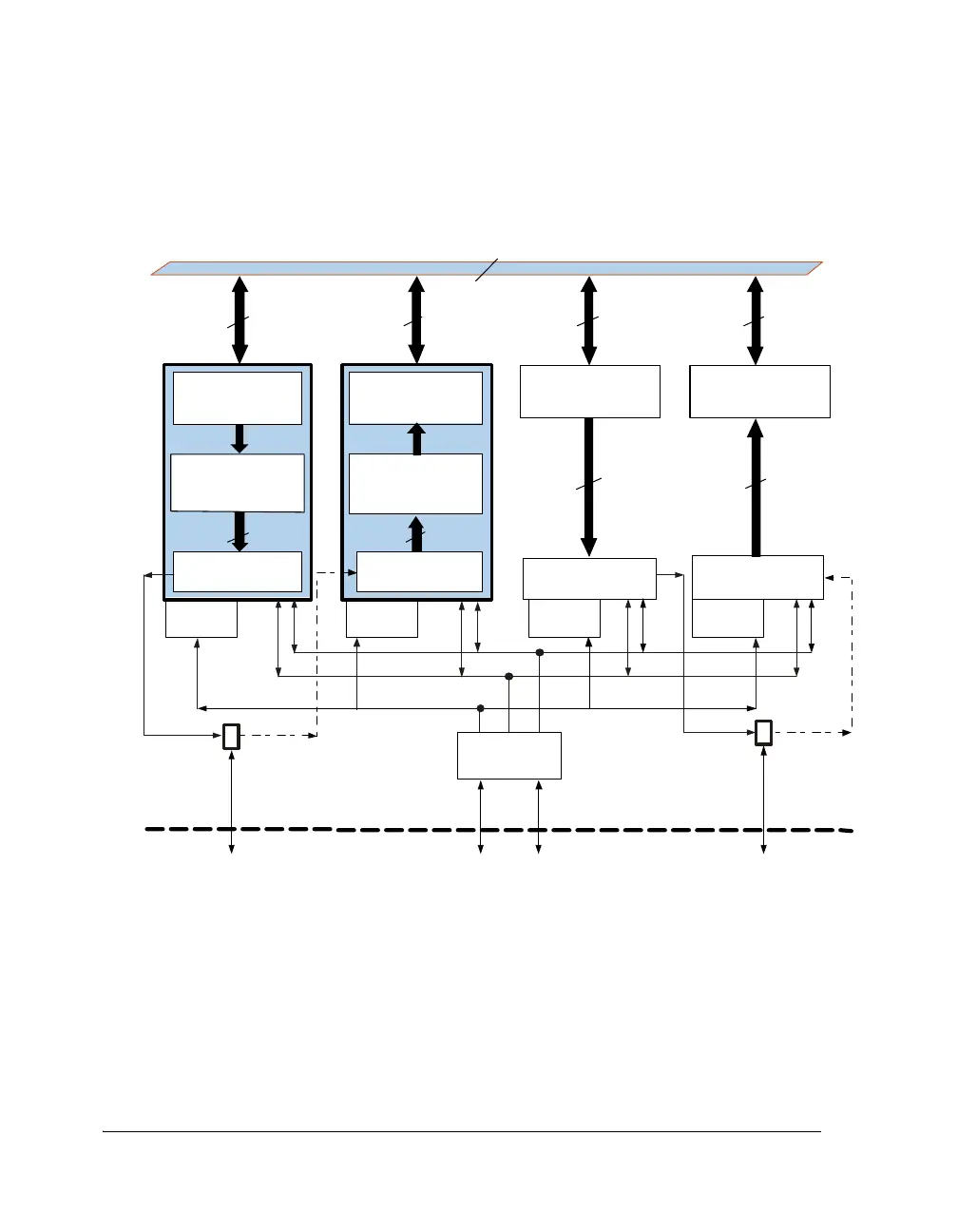

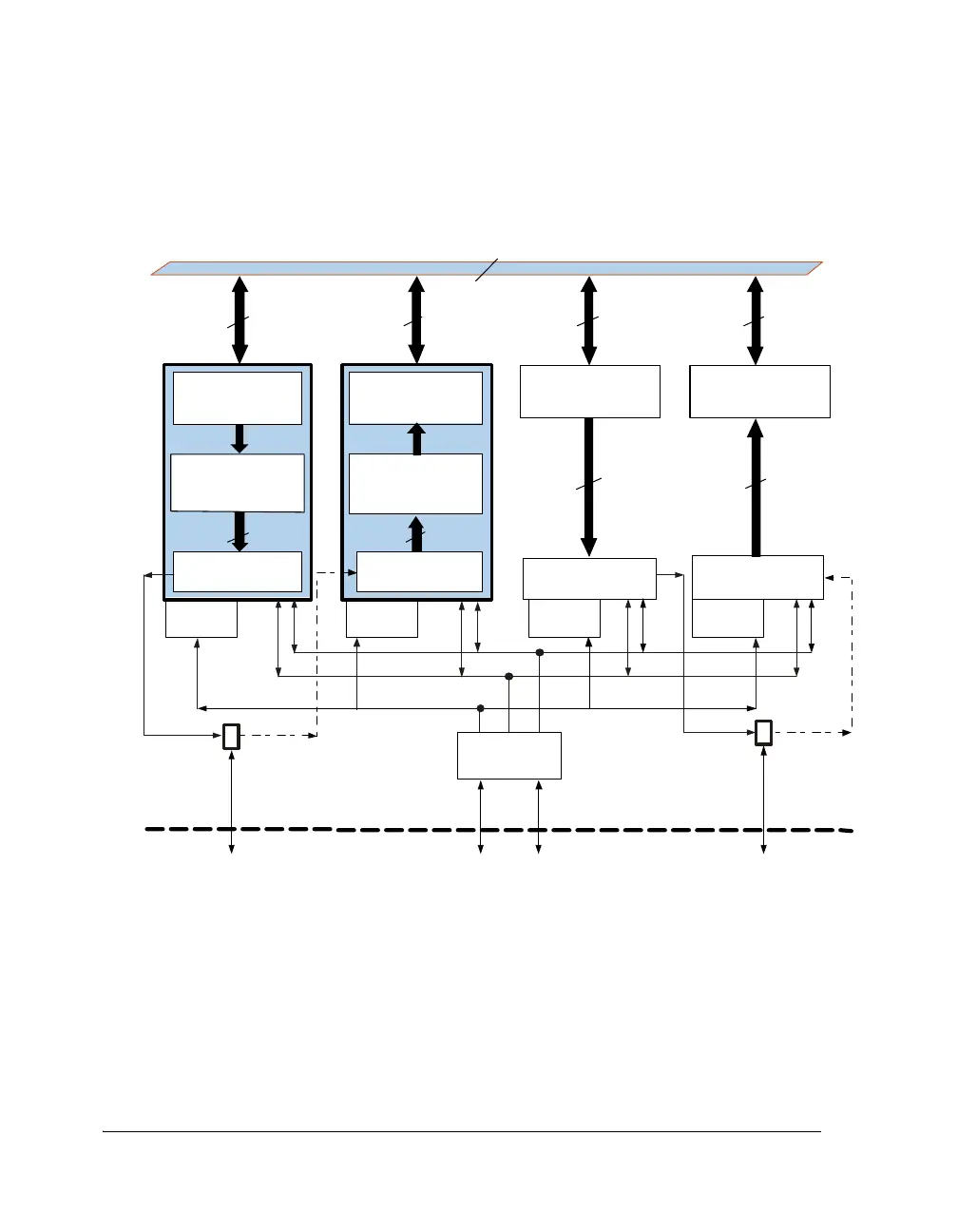

Figure 5-2. Serial Port Block Diagram

RXSPxA

RECEIVE DATA BUFFER

TXSPxB

TRANSMIT DATA BUFFER

HARDWARE

COMPANDING

(EXPANSION)

SPORTS 1, 3, 5 & 7 ONLY

RECEIVE SHIFT

RE GISTER

TXSPxA

TRANSMIT DATA

BUFFER

32

RXSPxB

RECEIVE DATA BUFFER

32 3232 3232

32

3232

32

3232

TRANSMIT SHIFT

REGISTER

TRANSMIT SHIFT

REGISTER

RECEIV E SHIFT

REGISTER

SERIAL PORT

CONTROL

SPORTX_DA SPORTX_CLKSPORTX_FS

DM DATA BUS

PM DATA BUS

I/O DATA BUS

SPORTX_DB

SPTRAN CNTL

SPORTX_CLK

SPORTX_FS

SPTRAN=1

TX ENABLE

SPTRAN=0

RX ENABLE

SPORTX_DA_OUT SPORTX_DA_IN

SPORTX_DB_OUT SPORTX_DB_IN

HARDWARE

COMPANDING

(COMPRESSION)

SPORTS 0, 2, 4 & 6 ONLY

SPTRAN=1

TX ENABLE

SPTRAN=0

RX ENABLE

Loading...

Loading...