ADSP-21368 SHARC Processor Hardware Reference 8-9

Pulse Width Modulation

The resulting on-times (active low) of the PWM signals over the full

PWM period (two half periods) produced by the PWM timing unit and

illustrated in Figure 8-3 on page 8-11 may be written as:

The range of T

AH

is:

and the corresponding duty cycles are:

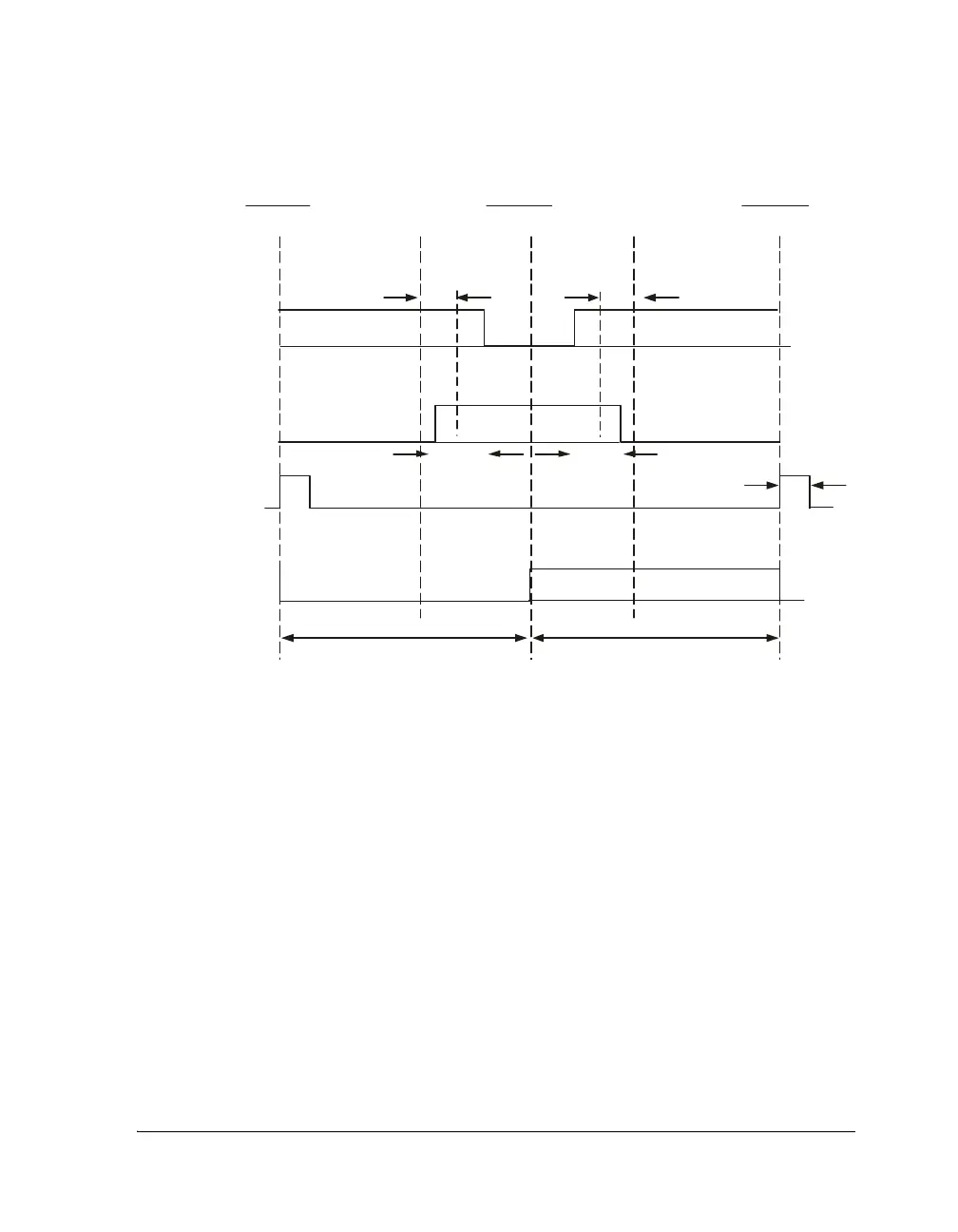

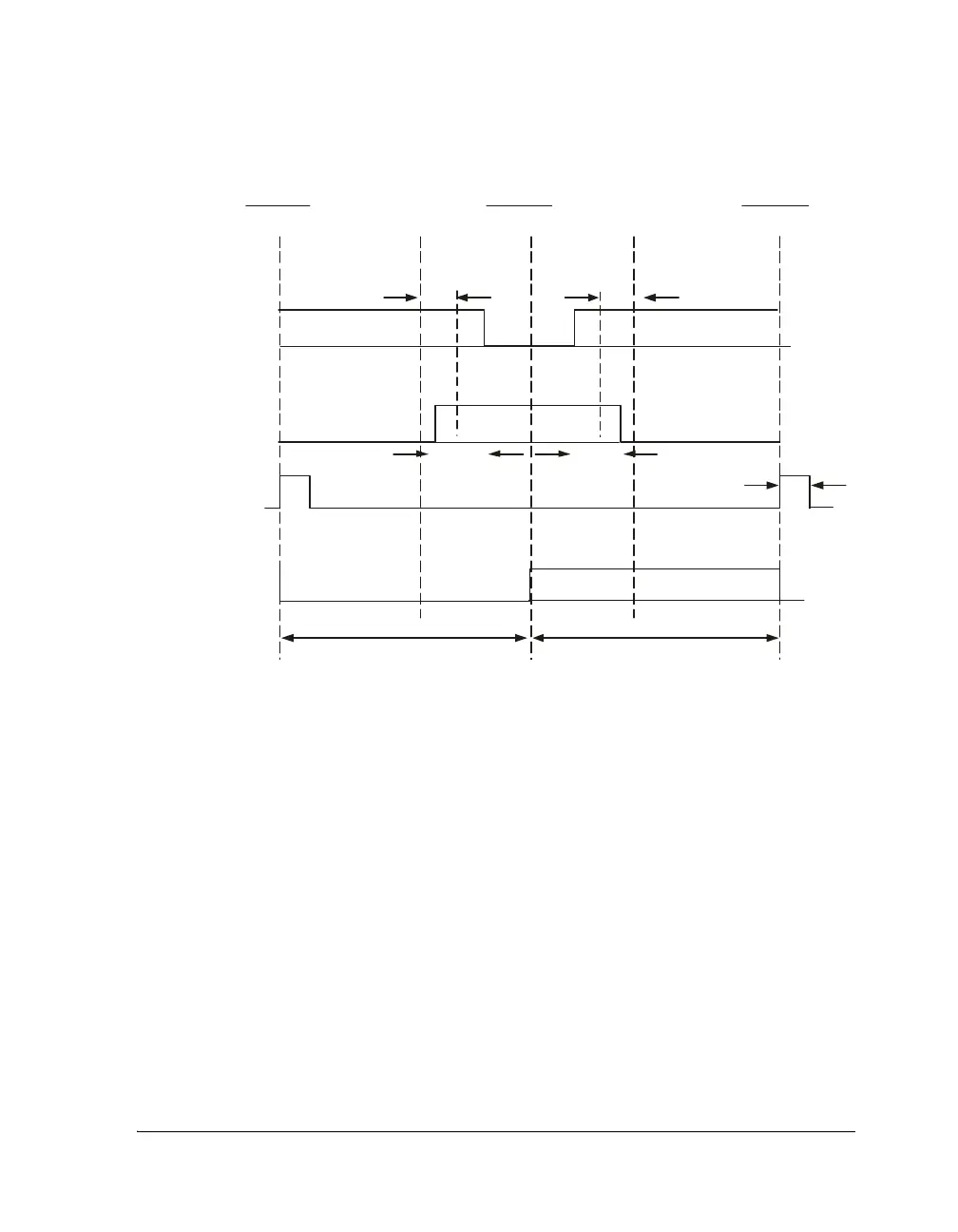

Figure 8-2. Center-Aligned Paired PWM in Single-Update Mode,

Low Polarity

......................

.....

......................

.....

PWMPERIOD PWMPERIO D

PWMCHA

PWMCHA

PWMPERIOD

2

+

0

PWMPERIO D

2

_

PWMPERIOD

2

+

0

2xPWMDT 2xPWMDT

PWMSYNCWT + 1

count

pwm_ah

pwm_al

PWMPHASE

pwm_pwmsync_out

02– PWMPERIOD t

PCLK

]××[

T

AH

PWMPERIOD 2 PWMCHA PWMDT)+(× t

PCLK

×–(=

Loading...

Loading...