ADSP-21368 SHARC Processor Hardware Reference 14-29

System Design

To determine switching frequencies for the serial ports, divide down the

internal clock, using the programmable divider control of each port (

DIVx

for the serial ports). For the SPI port, the BAUDR bit in the SPICTL register

controls the SPICLK baud rate based on the core clock frequency.

Note the following definition and Figure 14-8 for various clock periods

that are functions of

CLKIN and the appropriate ratio control:

CCLK = core clock = PLLICLK × PLL multiply ratio (determined by CLK_CFG

pins)

Programs can modify this setting using bits in the

PMCTL register. For more

information, see “Power Management Control Register (PMCTL)” on

page A-170.

L

Performing a hard reset on the processor also resets the PLL.

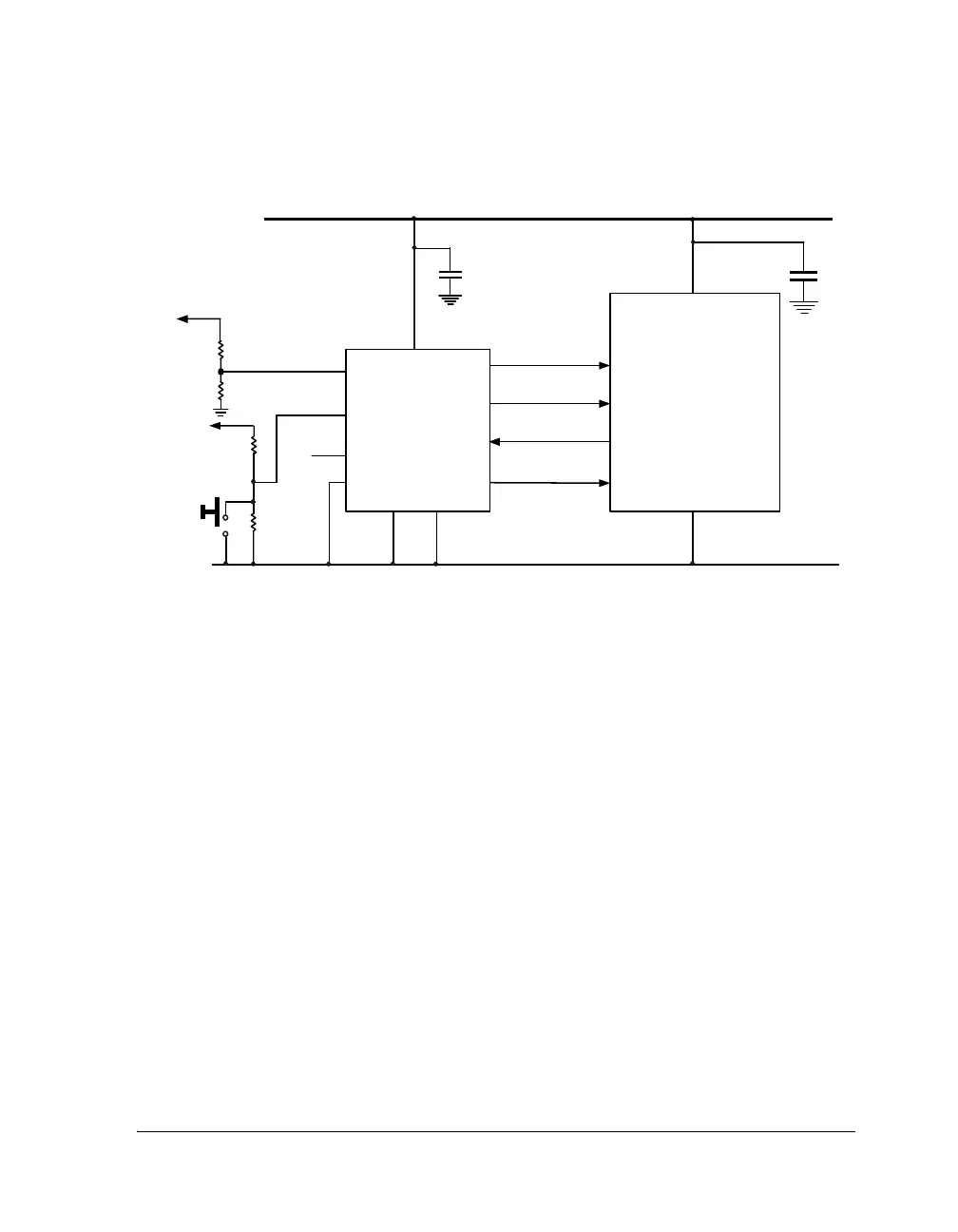

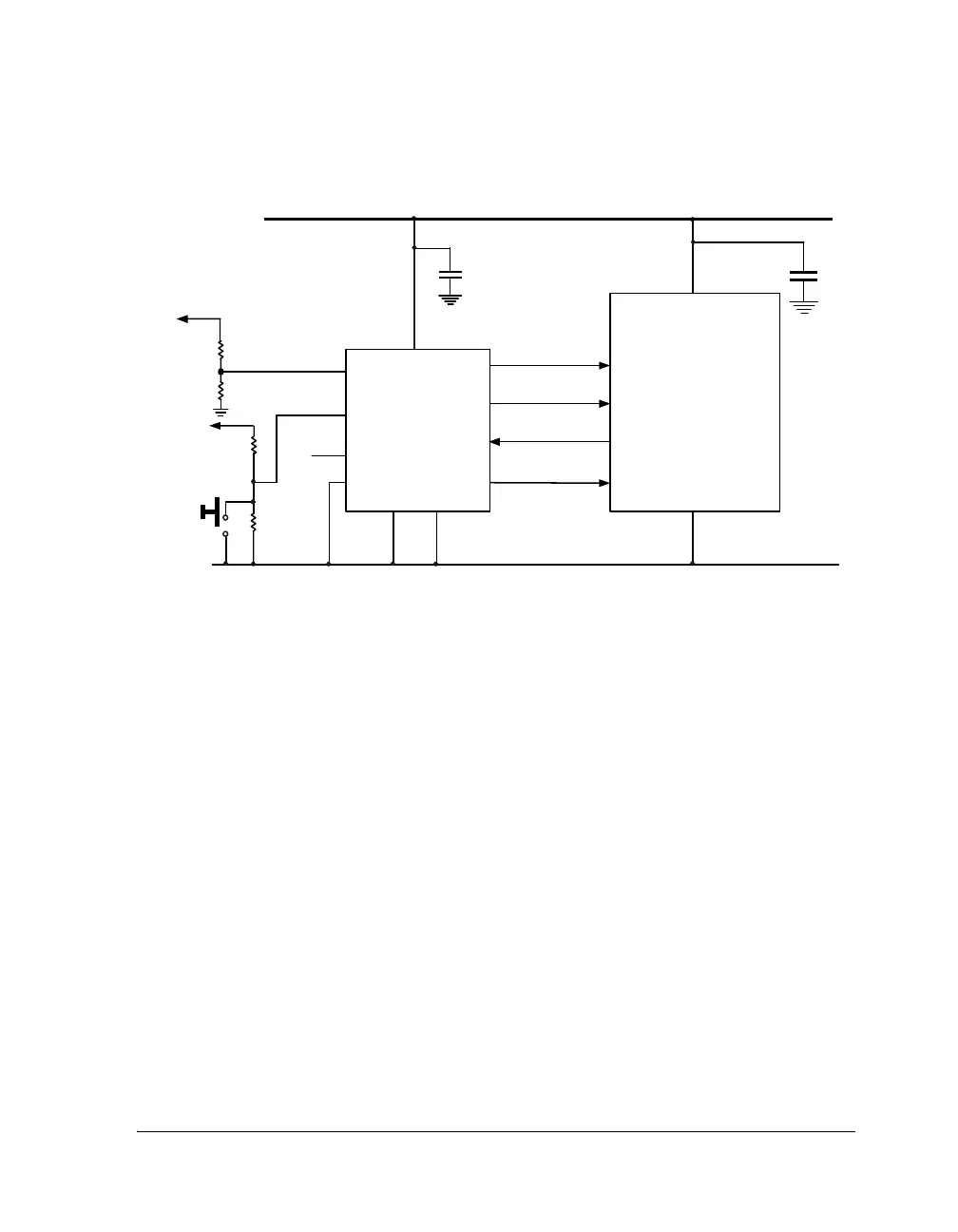

Figure 14-7. Reset Generator and Power Supply Monitor

RESET

NMI

IRQx

FLAGx

GND

RESET

V

DDEXT

PFI

OSCSEL

PFO

WDI

WDO

4

8

7

15

11

14

ADM8697

V

CC

9

RST

10

DDEXT

+

.

a

ADSP-213xx

S

3

15

OSCIN

GND TST

LL

W

NC

3.3V

V

t

>1.3V

V

t

>1.3V

V

LINE SENSE

Loading...

Loading...