Clock Derivation

14-30 ADSP-21368 SHARC Processor Hardware Reference

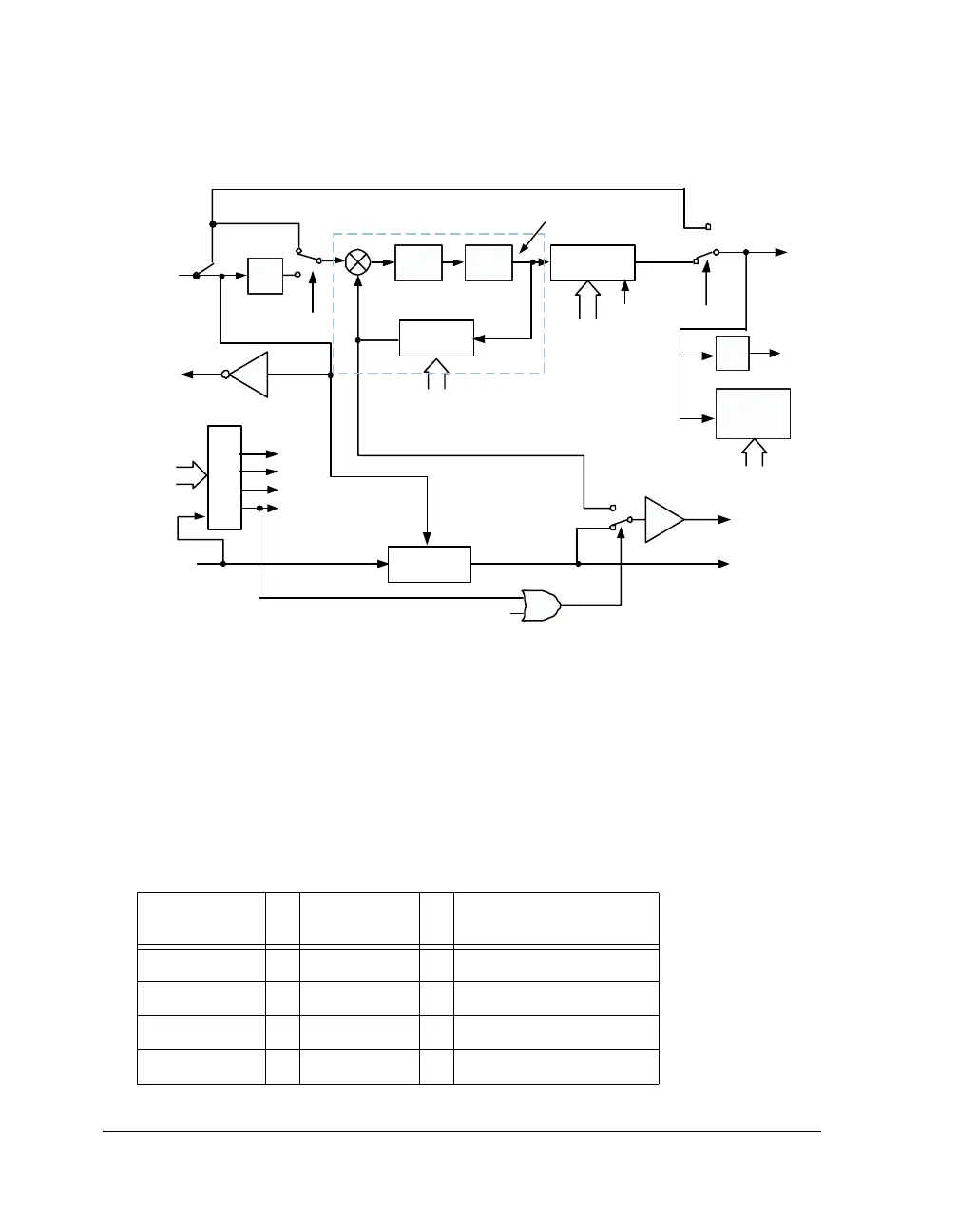

Figure 14-8. Core Clock and System Clock Relationship to CLKIN

Table 14-5. CLKOUT and CCLK Clock Generation Operation

Timing

Requirements

Calculation Description

CLKIN = 1/t

CKIN

=Input Clock

CLKOUT = 1/t

TCK

= Local Clock Out

PLLICLK = 1/t

PLLIN

= PLL Input Clock

CCLK = 1/t

CCLK

= Core Clock

÷2

+

–

0

1

INDIV[8]

LOOP

FILTER

VCO

÷1,2,4,8

N

PLLD[7..6]

DIVEN[9]

01

1

PLLBP[15]

AM P

÷1

-

64

M

PLLM[5 ..0]

C

L

K

_

C

F

G

[

1

.

.

0

]

00= x6

01 = x32

10 = x16

11= x6

DELAY

4096x CLKIN

CLKOUTEN[12]

BUFF

÷2

0

1

CCLK

100 MHz

to

400 MHz

PCLK

(IOP)

CLKOUT

or

CORERST

RESETOUT

CLKIN

(see data sheet)

RESET

XTAL

BOOT CLKCFG[]->PLLM[] CFG

Notes

1 . C LKO UT i s mux ed wit h RESETOUT. After r es et, RESETOUT is selected . CLKOUT is selected by setting bit 12 in the PMCTL r egister.

2.The PLL ratio is controlled by the states of the CLKCFG[1:0] pins at reset and can be modified in software throu gh the

PLLMand PLLDx bits in the PMCTL register.

3.To place thePLL in bypass mode, set bit 15 in the PMCTL register. (CCLK = PLLICLK when set.)

4. Programs can interrupt the internal clocksource to each of the following peripherals: timer,SPI,SPORTs, and parallel port.

These internal clock sources a re dis abled at reset and are enable d and l eft e nabled after each pe ripher al is enabled.

Note that thes e peripherals DO NOT RUN at the core cl ock freq ue ncy. For more information please see the respective periphe ral

chapters in theADSP -2 136x SHARC Processor Hardware Reference .

.Pl

as

f

to th

o

sso

s

ifi

data sh

ts fo

ma xi mum CLKI N and

stal sou

s

ifi

ations.

160 MHz < VCO_OUT < 800 MHz

÷2 , 2 .5,

3, 3.5, 4

SDCLK

SDRATIO[20..18]

P LL BYP ASS; R eserved

C

L

K

C

F

G

[

1

.

.

0

]

MULTIPLIER

BLOCK

Loading...

Loading...