ADSP-21368 SHARC Processor Hardware Reference 14-31

System Design

Table 14-7 describes clock ratio requirements. Table 14-8 shows an exam-

ple clock derivation.

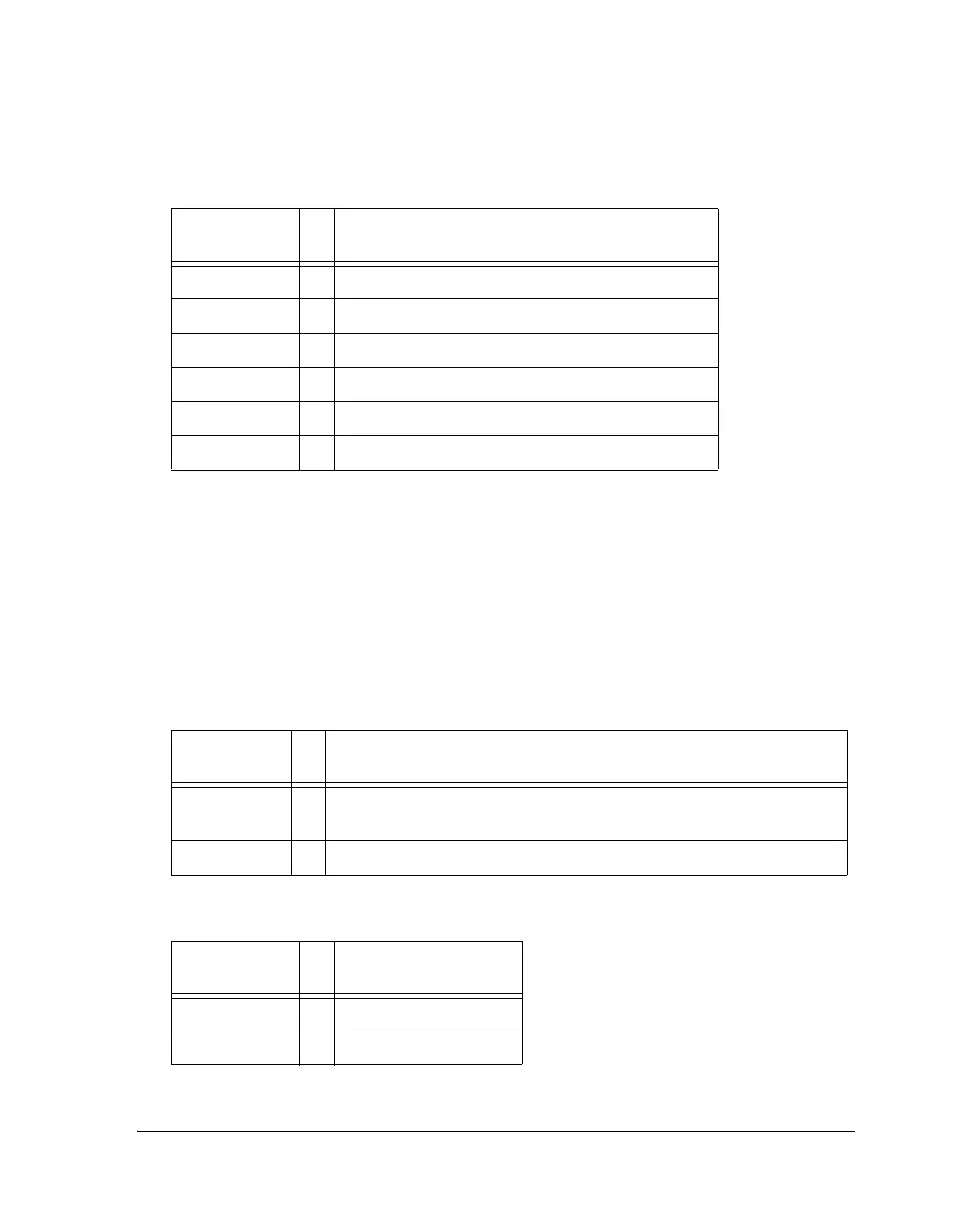

Table 14-6. Clock Relationships

Timing

Requirements

Description

1

t

CK

= CLKOUT Clock Period

t

PLLICK

= PLL Input Clock

t

CCLK

= Core Clock Period (Processor)

t

PCLK

= Peripheral Clock Period = 2 × t

CCLK

t

SCLK

= Serial Port Clock Period = (t

PCLK

) × SR

t

SPICLK

= SPI Clock Period = (t

CCLK

) * SPIR

1 where:

SR = serial port-to-core clock ratio (wide range, determined by CLKDIV)

SPIR = SPI-to-core clock ratio (wide range, determined by SPICTL register)

SCLK = serial port clock

SPICLK = SPI clock

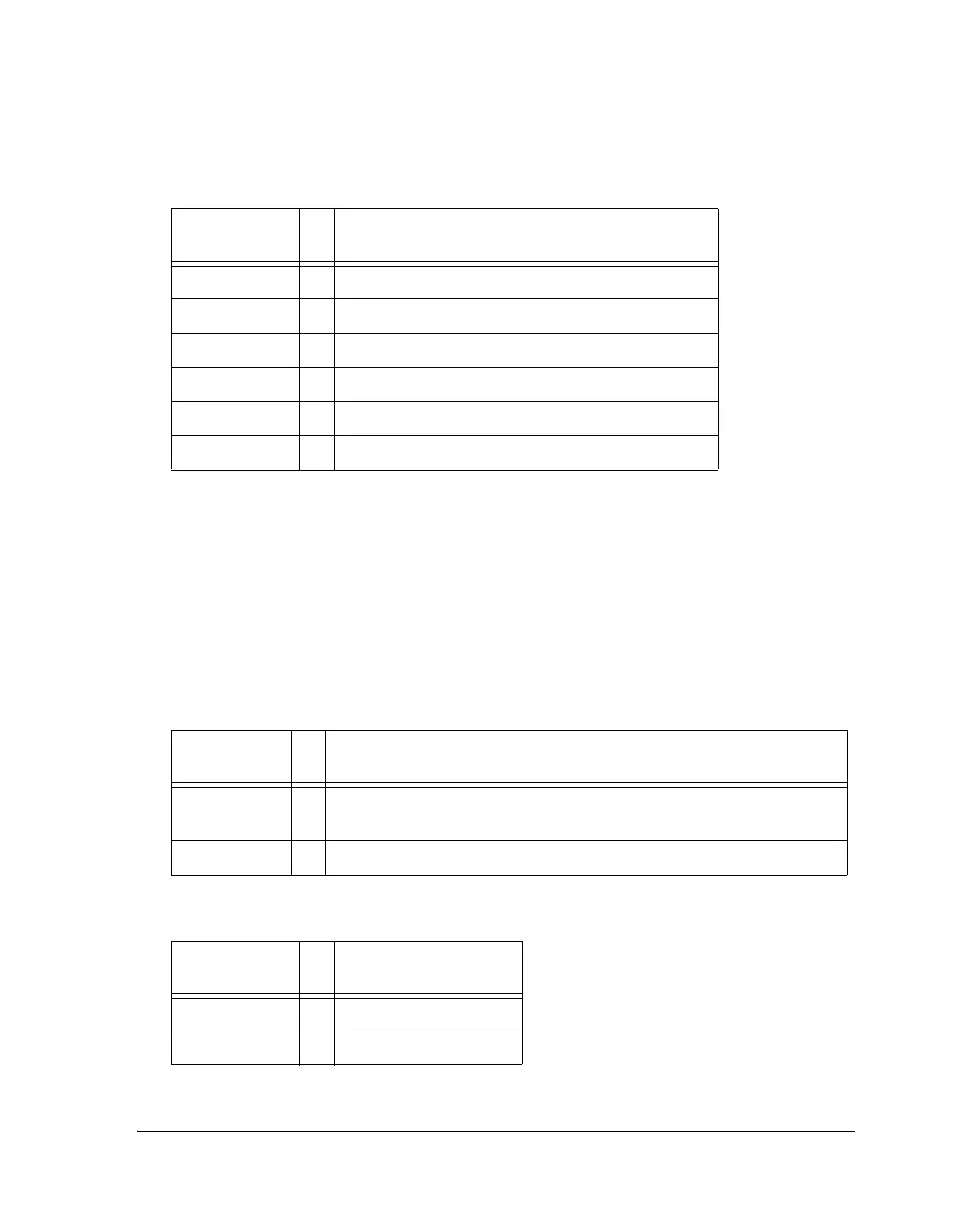

Table 14-7. Clock Ratios

Timing

Requirements

Description

c

RTO

= Core to CLKOUT ratio (3:1, 8:1, or 16:1, determined by CLK_CFGx

pins at reset). Programs can modify this ratio using the PMCTL register.

s

RTO

= Sport:core clock ratio (wide range determined by xCLKDIV)

Table 14-8. Clock Derivation

Timing

Requirements

Description

t

CCLK

=(t

CK

) × cRTO

t

SCLK

=(t

CCLK

) × sRTO

Loading...

Loading...