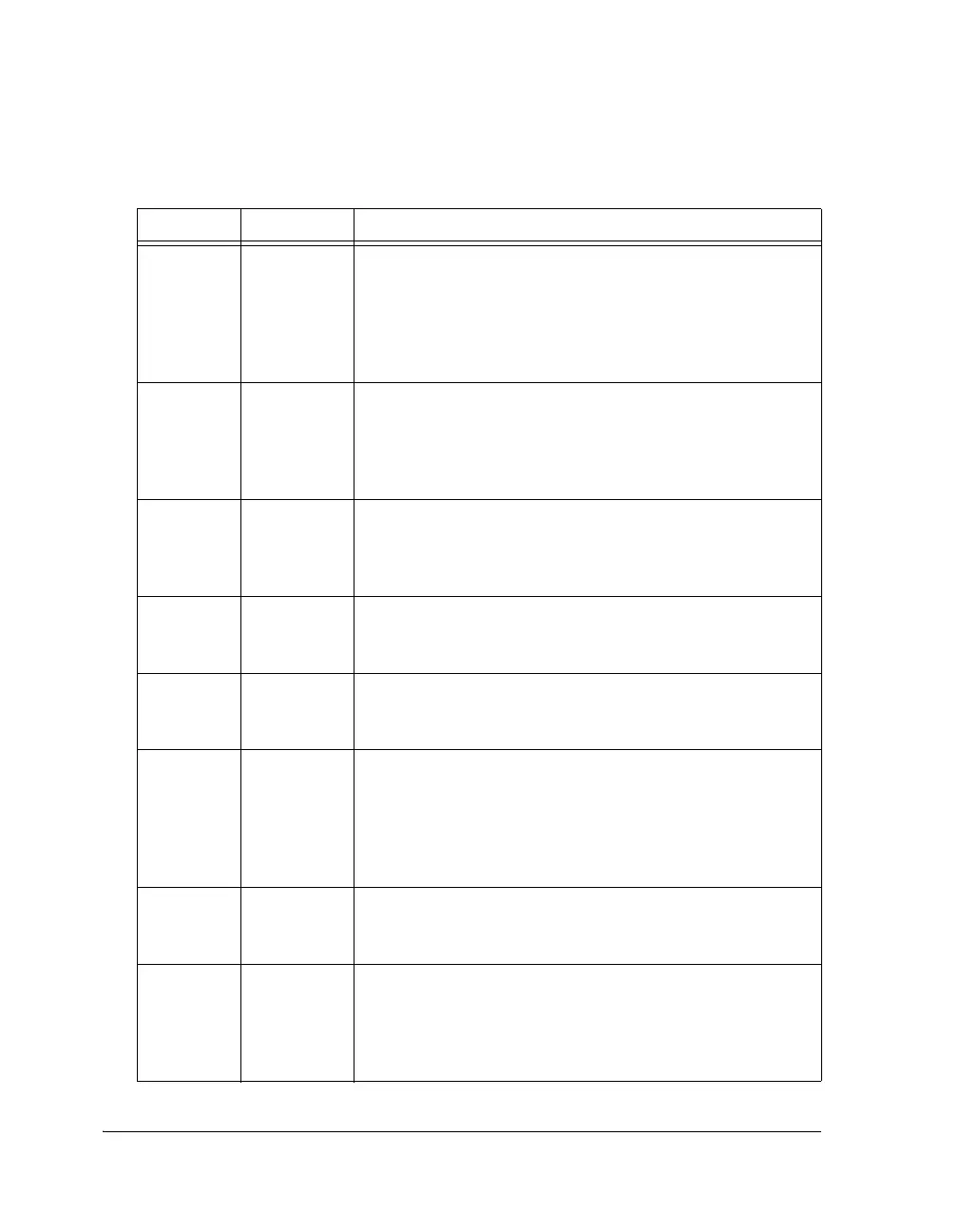

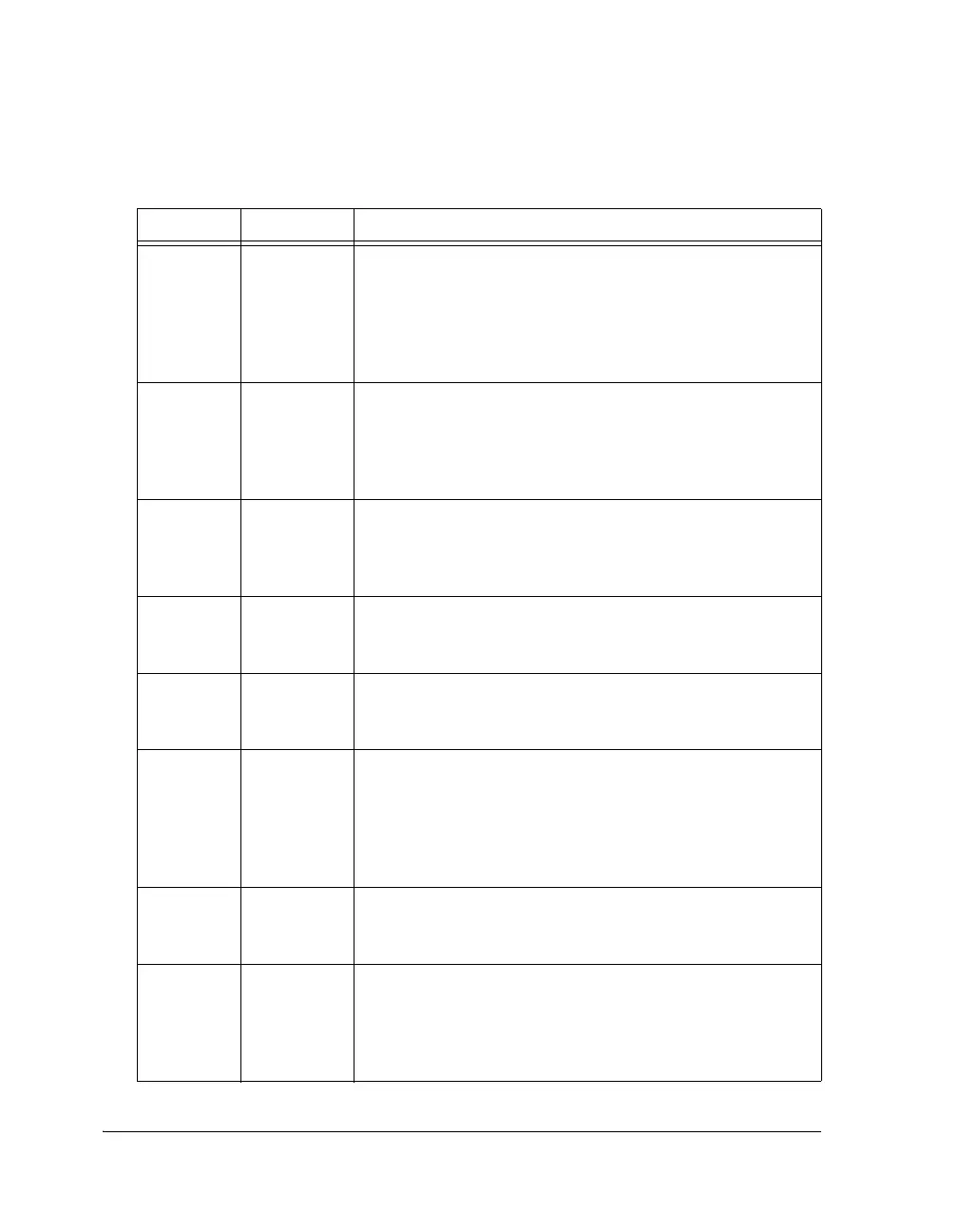

External Port Registers

A-24 ADSP-21368 SHARC Processor Hardware Reference

16 X16DE SDRAM External Data Path Width. Selects whether the

SDRAM interface is 32 or 16 bits wide.

If X16DE = 0, DATA31–0 should be connected to the SDRAM.

If X16DE = 1, DATA15–0 should be connected to the SDRAM

and 16 to 32-bit packing is performed. (Valid for all processors

except for the ADSP-21375 processor).

18–17 SDTWR SDRAM tWR Specification. tWR = 1–3 SDCLK cycles. Based

on the system clock frequency and the timing specifications of

the SDRAM used. Programmed parameters apply to all four

banks in the external memory.

See t

WR

on page 3-35.

19 SDORF Optional Refresh.

1 = Auto refresh not performed

0 = Auto refresh occurs when refresh counter expires

(see “Auto-Refresh” on page 3-70).

20 Force AR Force Auto Refresh.

1 = Force auto refresh

0 = No effect

21 Force PC Force Precharge.

1 = Force precharge

0 = No effect

22 Force LMR Force Load Mode Register Write. This command performs a

load mode register command immediately. This is in contrast to

the normal load mode register set which requires some delay. This

command performs a precharge all (if not precharged already)

followed by a mode register write. (Valid for ADSP-2137x pro-

cessors only).

23 SDBUF Pipeline Option with External Register Buffer.

1 = External SDRAM CTL/ADDR control buffer enable

0 = No buffer option

26–24 SDTRCD SDRAM tRCD Specification. t

RCD

= 1–7 SDCLK cycles. Based

on the system clock frequency and the timing specifications of

the SDRAM used. Programmed parameters apply to all four

banks in the external memory.

See t

RCD

on page 3-35.

Table A-6. SDRAM Control Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...