ADSP-21368 SHARC Processor Hardware Reference A-23

Register Reference

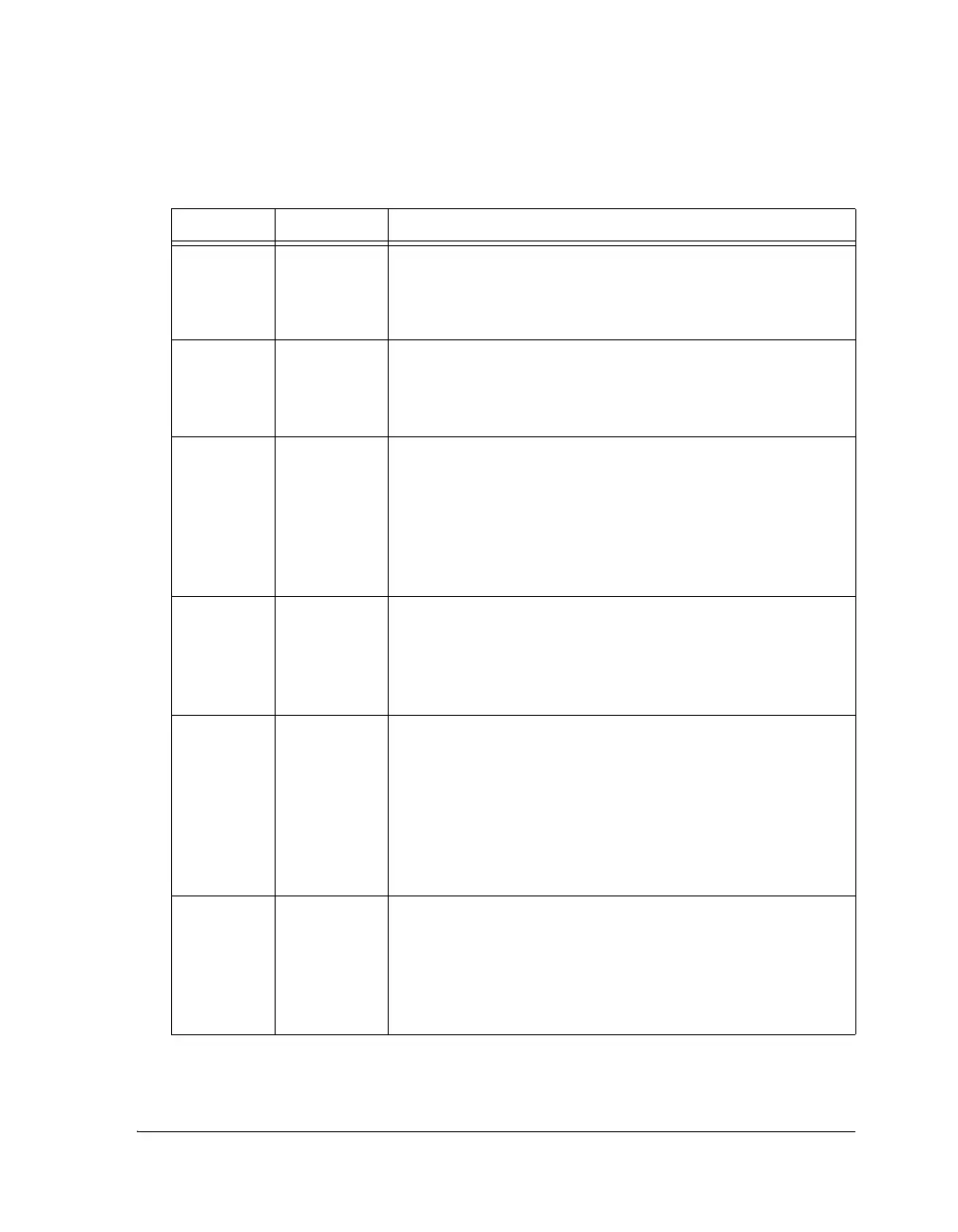

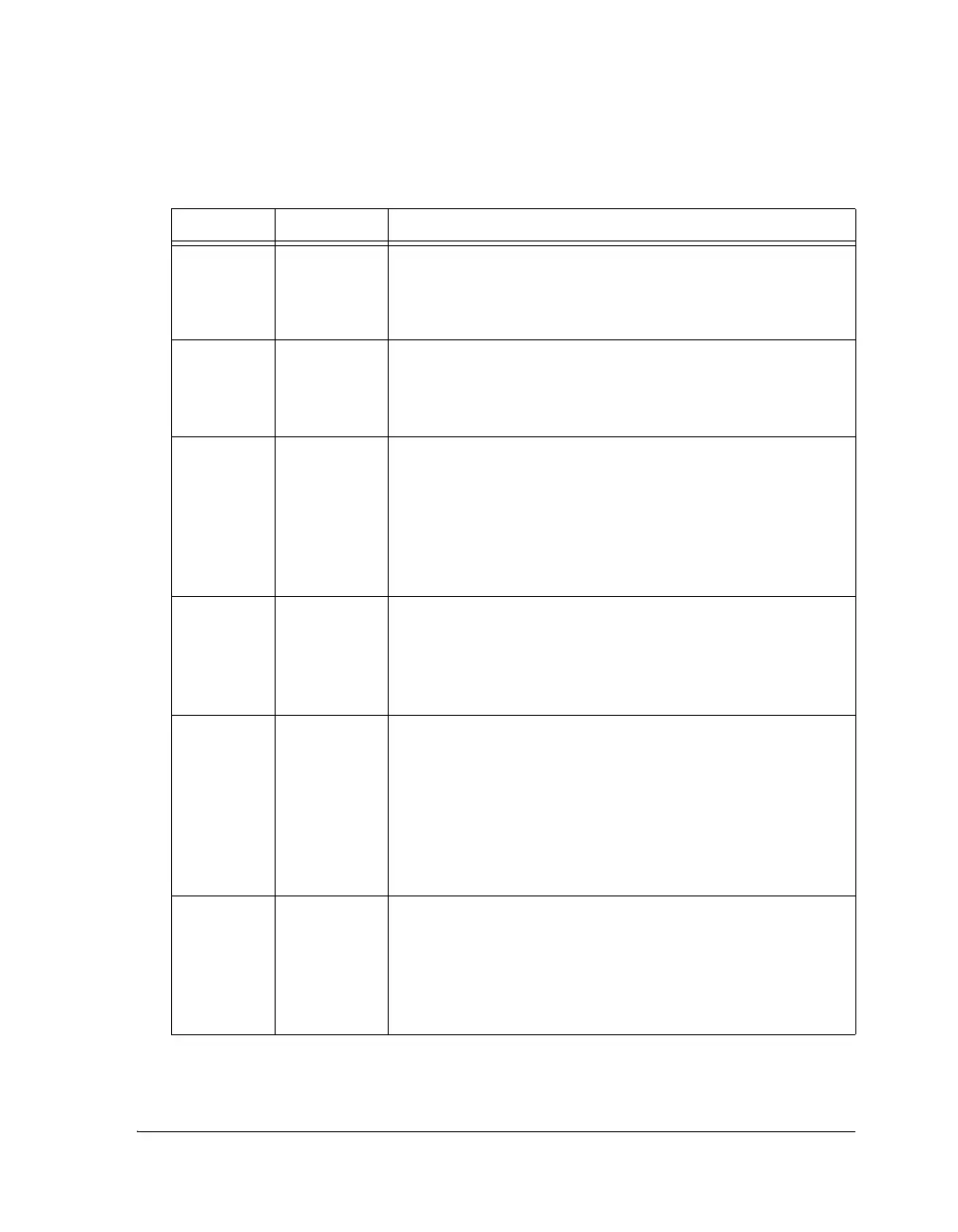

7–4 SDTRAS tRAS Specification. Based on the system clock frequency and the

timing specifications of the SDRAM used. Programmed parame-

ters apply to all four banks in the external memory.

See t

RAS

on page 3-35.

10–8 SDTRP tRP Specification. Based on the system clock frequency and the

timing specifications of the SDRAM used. Programmed parame-

ters apply to all four banks in the external memory.

See t

RP

on page 3-35.

11 SDPM SDRAM Power-Up Mode. The SDPM and SDPSS bits work

together to specify and trigger an SDRAM power-up (initializa-

tion) sequence. If the SDPM bit is set (=1), the SDC does a pre-

charge all command, followed by a load mode register command,

followed by eight auto-refresh cycles. If the SDPM bit is cleared

(=0), the SDC does a precharge all command, followed by eight

auto-refresh cycles, followed by a load mode register command.

13–12 SDCAW SDRAM Bank Column Address Width.

00 = 8 bits

01 = 9 bits

10 = 10 bits

11 = 11 bits

14 SDPSS SDRAM Power-Up Sequence Start. The power-up sequence

occurs and is followed immediately by the read or write transfer

to SDRAM that is used to trigger the SDRAM power-up

sequence. Note that there is a long latency for this first access to

SDRAM because the SDRAM power-up sequence takes many

cycles to complete.

1 = Enable power-up on next SDRAM access

0 = No effect

15 SDSRF Self Refresh Enable. When the SDSRF bit is set to 1, self-refresh

mode is triggered. Once the SDC completes any active transfers,

the SDC executes the sequence of commands to put the SDRAM

into self-refresh mode. The next access to the enabled SDRAM

bank causes the SDC to execute the commands to exit from

self-refresh and execute the access.

Table A-6. SDRAM Control Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...