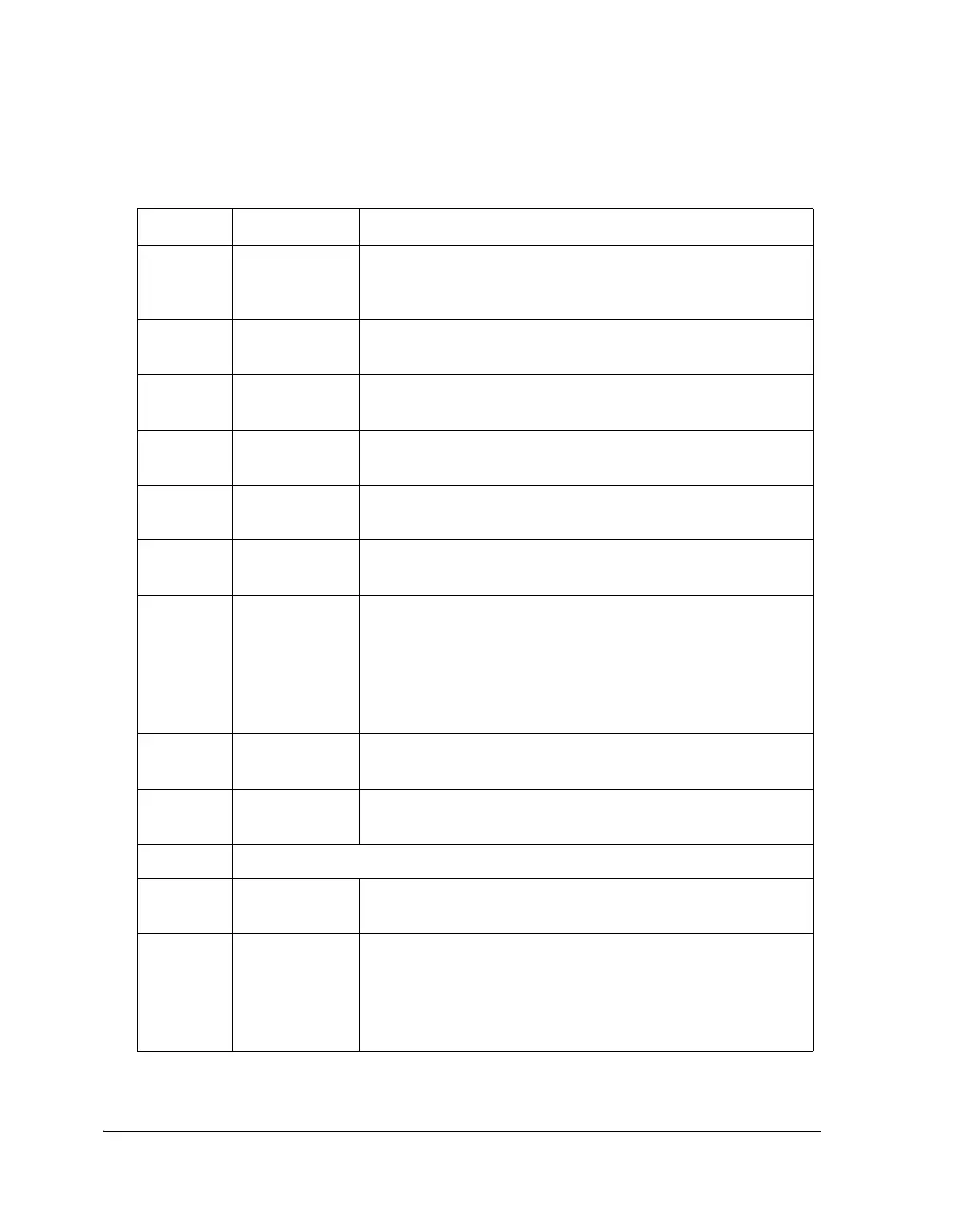

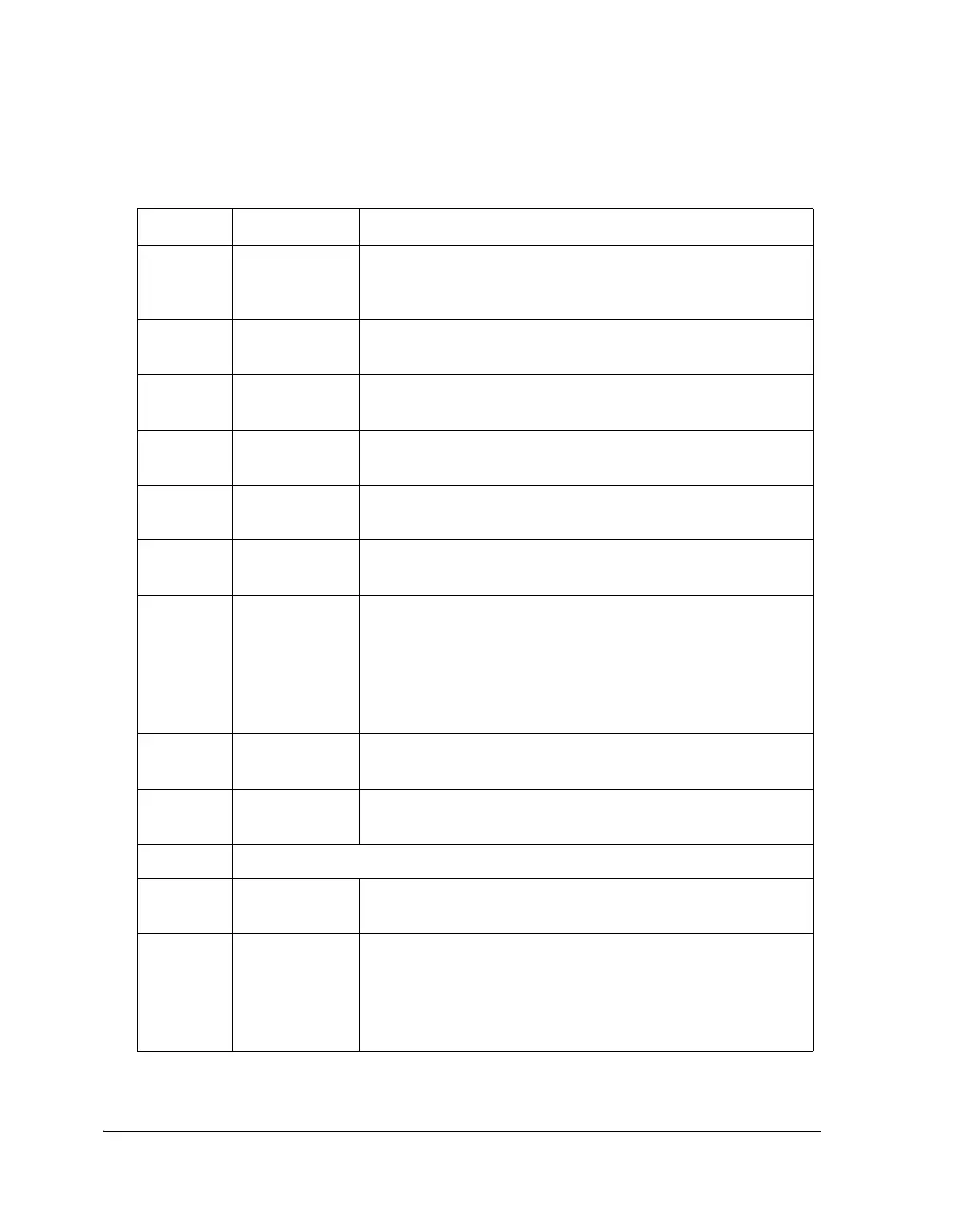

Hardware Breakpoint Control Register

A-178 ADSP-21368 SHARC Processor Hardware Reference

13 NEGIA1 Negate Instruction Address Breakpoint #1.

0 = Do not negate breakpoint

1 = Negate breakpoint

14 NEGIA2 Negate Instruction Address Breakpoint #2.

For more information, see NEGPA1 bit description.

15 NEGIA3 Negate Instruction Address Breakpoint #3.

For more information, see NEGPA1 bit description.

16 NEGIA4 Negate Instruction Address Breakpoint #4.

For more information, see NEGPA1 bit description.

17 NEGIO1 Negate I/O Address Breakpoint.

For more information, see NEGPA1 bit description.

18 NEGEP1 Negate EP Address Breakpoint.

For more information, see NEGPA1 bit description.

19 ENBPA Enable Program Memory Data Address Breakpoints.

The ENB bits enable each breakpoint group. Note that when

the ANDBKP bit is set, breakpoint types not involved in the

generation of the effective breakpoint must be disabled.

0 = Disable breakpoints

1 = Enable breakpoints

20 ENBDA Enable Data Memory Address Breakpoints.

For more information, see ENBPA bit description.

21 ENBIA Enable Instruction Address Breakpoints.

For more information, see ENBPA bit description.

22 Reserved

23 ENBEP Enable External Port Address Breakpoint.

For more information, see ENBPA bit description.

24 ANDBKP AND Composite Breakpoints. Enables ANDing of each break-

point type to generate an effective breakpoint from the com-

posite breakpoint signals.

0 = OR breakpoint types

1 = AND breakpoint types

Table A-71. BRKCTL Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...