Enhanced Emulation Status Register

A-180 ADSP-21368 SHARC Processor Hardware Reference

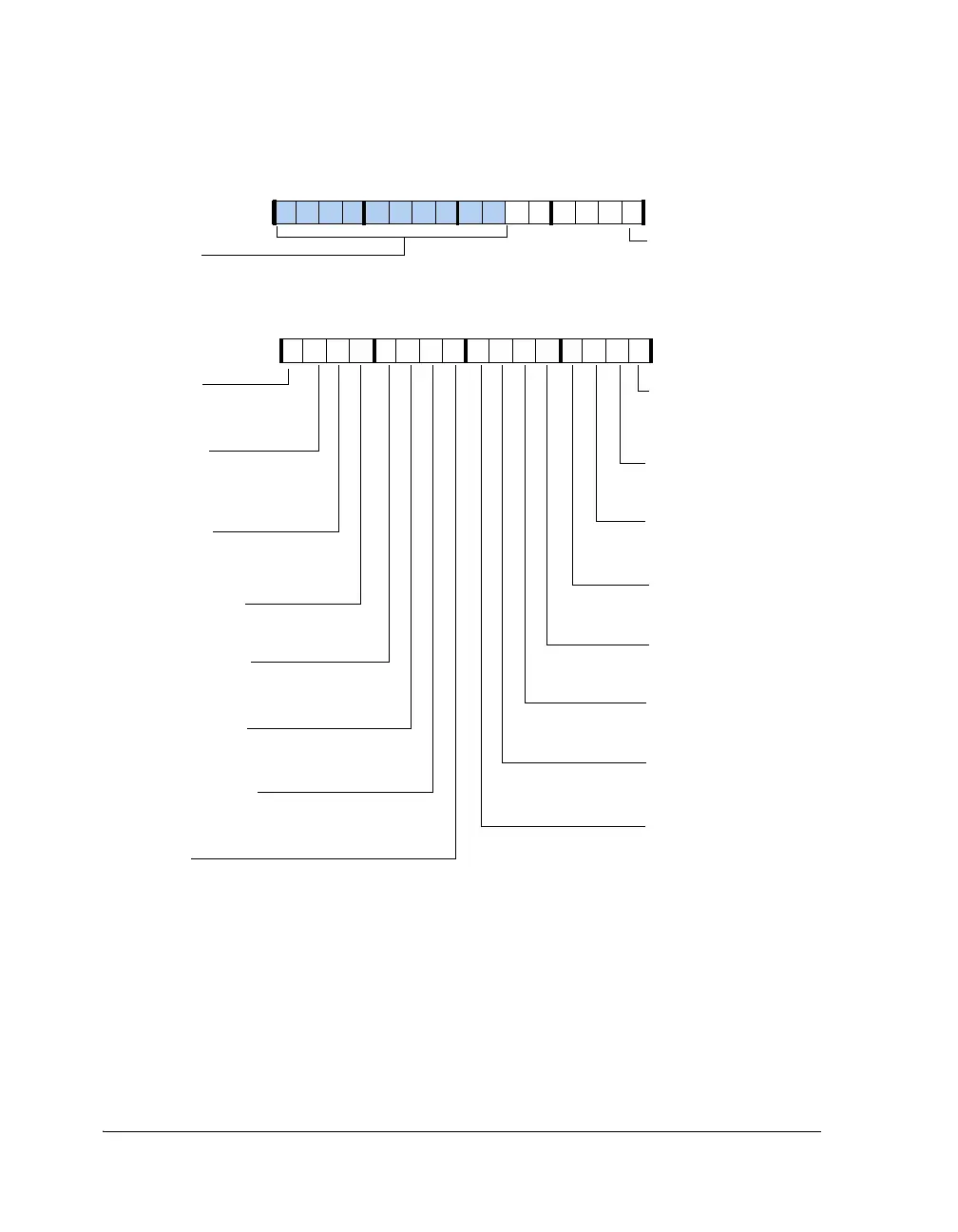

Figure A-86. EEMUSTAT Register

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000000000000000

OSPIDENS

EEMUIN Interrupt Enable

1= EEMUIN interrupt enable

0= EEMUIN interrupt disable

EEMUINENS

Operating System Processor ID

Enable

1=OSPID Register enable

0=OSPID Register disable

EEMUENS

Enhanced Emulation Feature Enable

Status

1=Feature is enabled

0=Feature is disabled

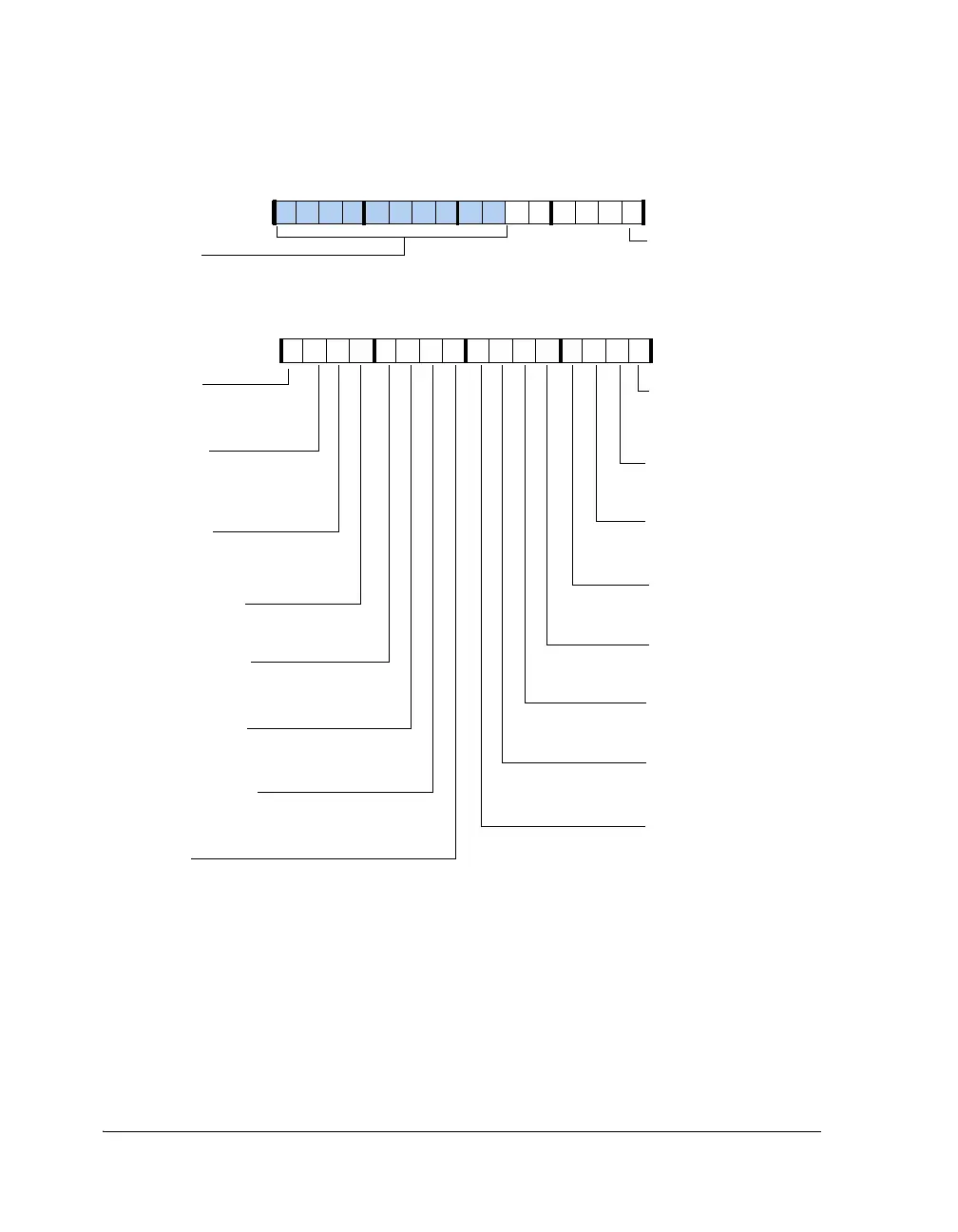

EEMUINFULL

EEMUOUTFULL

EEMUIN FIFO Full Status

1= EEMUIN FIFO full

0= EEMUIN FIFO is not full

EEMUOUTRDY

EEMUOUT FIFO Full Status

1= EEMUOUT FIFO full

0= EEMUOUT FIFO is not full

EEMUOUT Valid Data Status

1= EEMUOUT FIFO contains valid data

0= EEMUOUT FIFO is empty

EEMUOUTIRQEN

EEMUOUT Interrupt Enable

1= EEMUOUT interrupt enabled

0= EEMUOUT interrupt disabled

STATPA

Program Memory Break-

point Status

1=Break occurs

0=No break occurs

STATDA0

DM Breakpoint #0 Status

1=Break occurs

0=No break occurs

STATDA1

DM Breakpoint #1 Status

1=Break occurs

0=No break occurs

STATIA0

Instruction Breakpoint #0 Status

1=Break occurs

0=No break occurs

STATIA1

Instruction Breakpoint #1 Status

1=Break occurs

0=No break occurs

STATIA2

Instruction Breakpoint #2 Status

1=Break occurs

0=No break occurs

STATIA3

Instruction Breakpoint #3 Status

1=Break occurs

0=No break occurs

STATIO0

I/O Breakpoint #0 Status

1=Break occurs

0=No break occurs

STATEP

External Memory Breakpoint Status

1=Break occurs

0=No break occurs

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0000000000000000

STATIOY

Reserved

IOY Memory Breakpoint Status

0= No breakpoint occurs

1= Breakpoint occurs

EEMUSTAT

(0x30021)

Loading...

Loading...