ADSP-21368 SHARC Processor Hardware Reference A-181

Register Reference

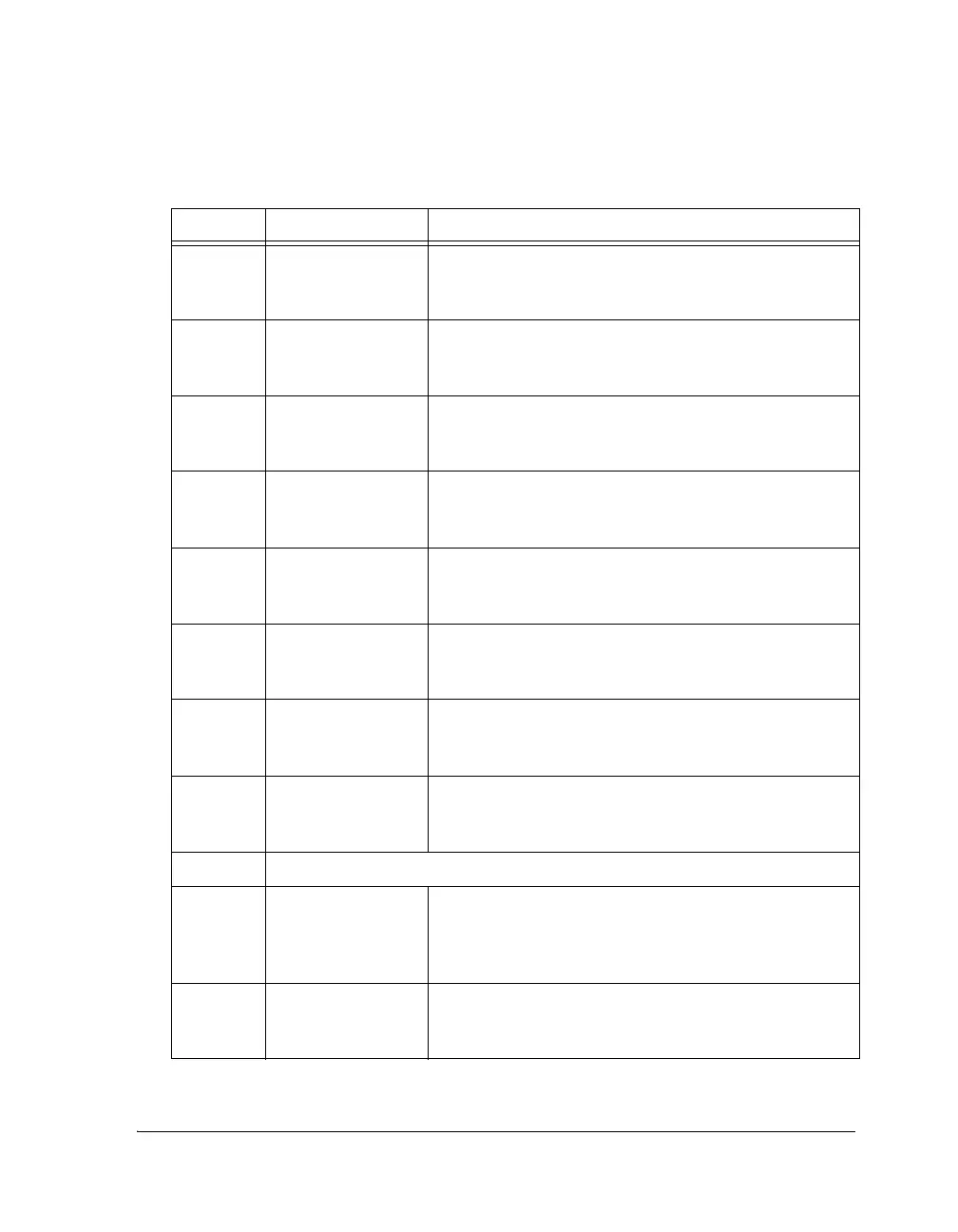

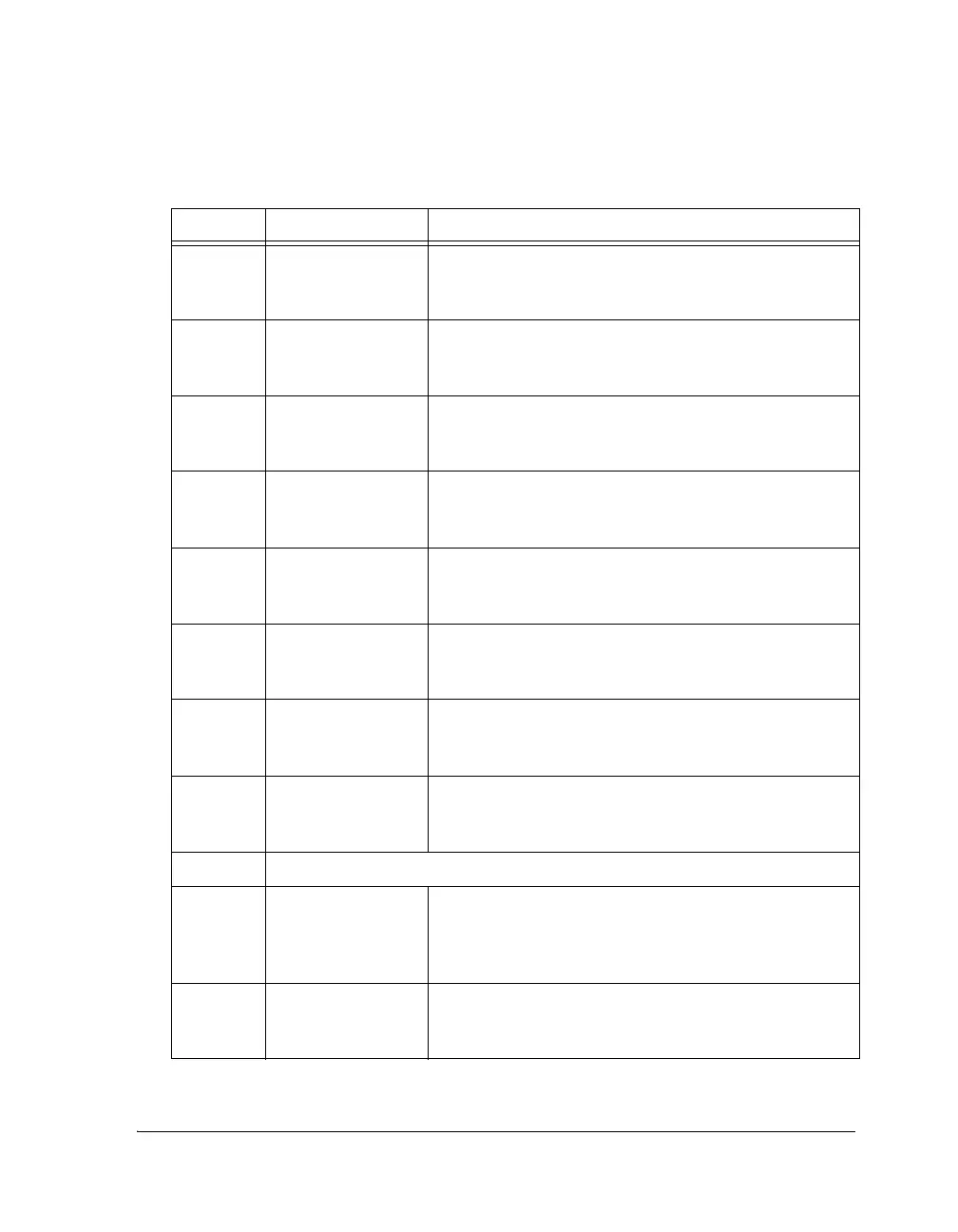

Table A-72. EEMUSTAT Register Bit Descriptions

Bit Name Description

0STATPA Program Memory Data Breakpoint Hit.

1

0 = No program memory breakpoint occurs

1 = Program memory breakpoint occurs

1STATDA0 Data Memory Breakpoint Hit.

1

0 = No data memory #0 breakpoint occurs

1 = Data memory #0 breakpoint occurs

2STATDA1 Data Memory Breakpoint Hit

.1

0 = No data memory #1 breakpoint occurs

1 = Data memory #1 breakpoint occurs

3STATIA0 Instruction Address Breakpoint Hit.

1

0 = No instruction address #0 breakpoint occurs

1 = Instruction address #0 breakpoint occurs

4STATIA1 Instruction Address Breakpoint Hit.

1

0 = No instruction address #1 breakpoint occurs

1 = Instruction address #1 breakpoint occurs

5STATIA2 Instruction Address Breakpoint Hit.

1

0 = No instruction address #2 breakpoint occurs

1 = Instruction address #2 breakpoint occurs

6STATIA3 Instruction Address Breakpoint Hit.

1

0 = No instruction address #3 breakpoint occurs

1 = Instruction address #3 breakpoint occurs

7STATIO I/O Address Breakpoint Hit.

1

0 = No I/OX address breakpoint occurs

1 = I/OX address breakpoint occurs

8Reserved

1

9 EEMUOUTIRQEN Enhanced Emulation EEMUOUT Interrupt Enable.

2

0 = EEMUOUT interrupt disable

1 = EEMUOUT interrupt enable

Note: Interrupts are of the low priority variety

10 EEMUOUTRDY Enhanced Emulation EEMUOUT Ready.

3

1 = EEMUOUT FIFO contains valid data

0 = EEMUOUT FIFO is empty

Loading...

Loading...