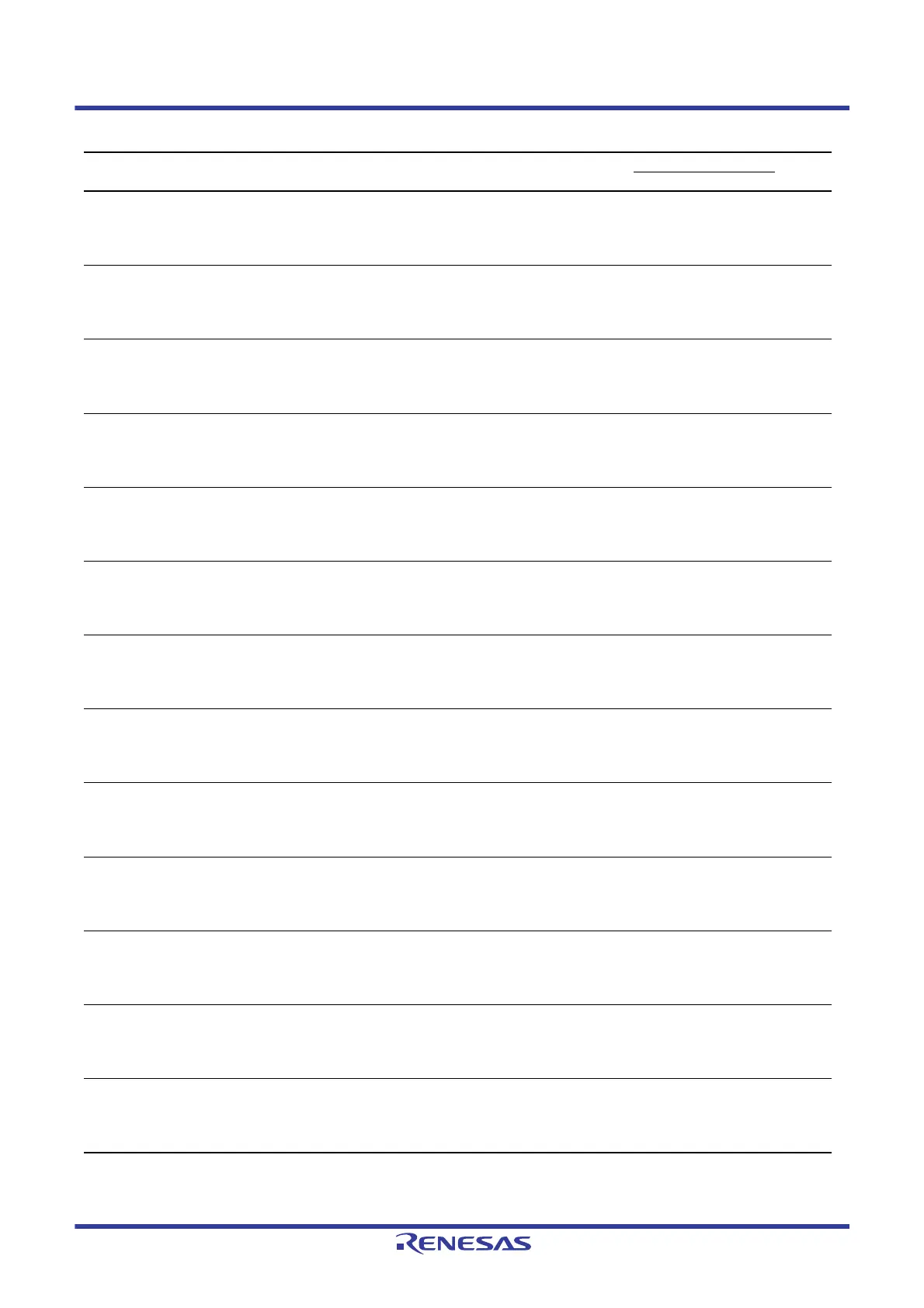

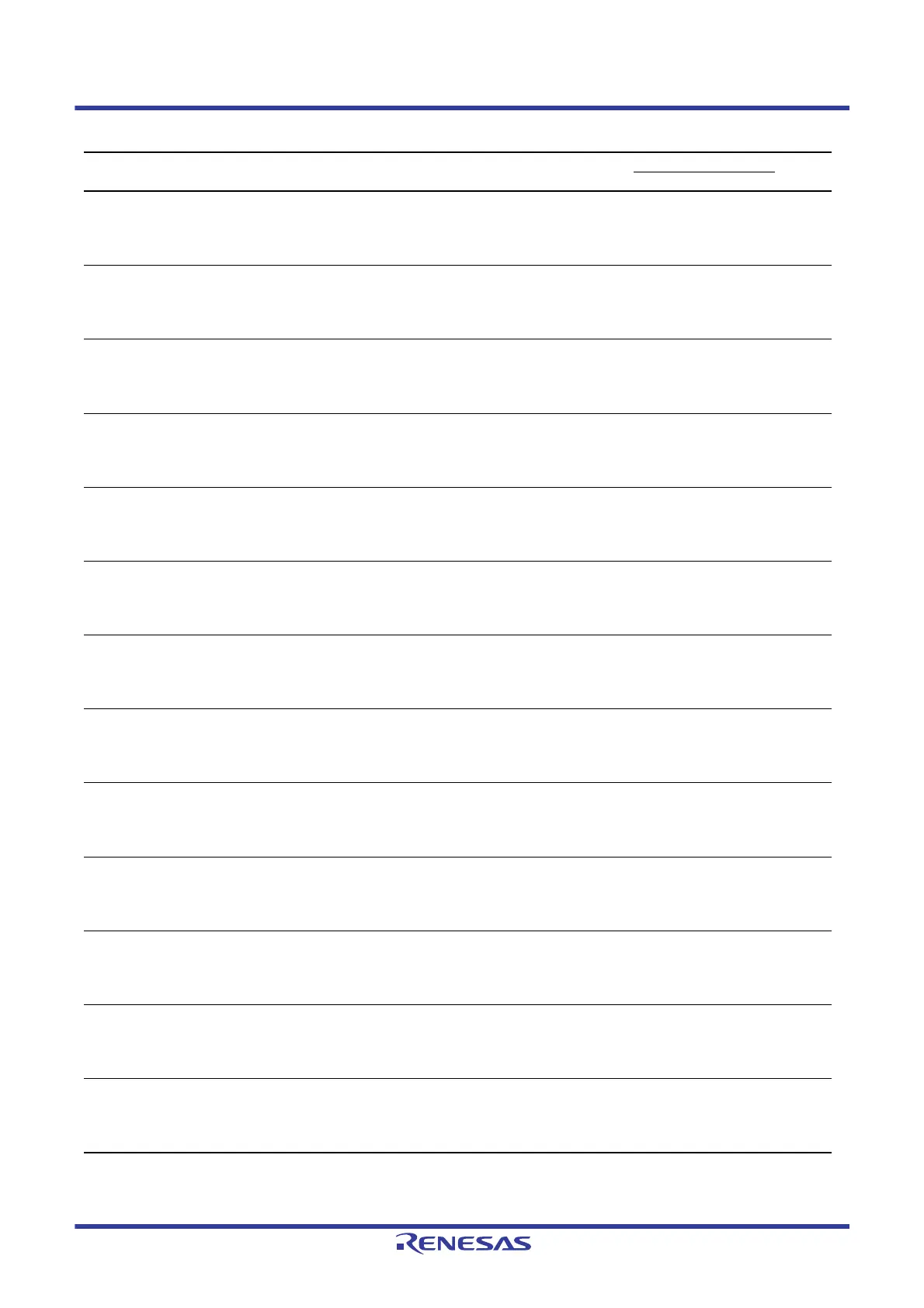

R01UH0823EJ0100 Rev.1.00 Page 115 of 1823

Jul 31, 2019

RX23W Group 5. I/O Registers

0008 AC20h SDHI Response Register 32 SDRSP32 32 32 3 or 4 PCLKB

cycles when

reading,

2 or 3 PCLKB

cycles when

writing

3 ICLK cycles

when reading,

2 ICLK cycles

when writing

section 40.

0008 AC28h SDHI Response Register 54 SDRSP54 32 32 3 or 4 PCLKB

cycles when

reading,

2 or 3 PCLKB

cycles when

writing

3 ICLK cycles

when reading,

2 ICLK cycles

when writing

section 40.

0008 AC30h SDHI Response Register 76 SDRSP76 32 32 3 or 4 PCLKB

cycles when

reading,

2 or 3 PCLKB

cycles when

writing

3 ICLK cycles

when reading,

2 ICLK cycles

when writing

section 40.

0008 AC38h SDHI SD Status Register 1 SDSTS1 32 32 3 or 4 PCLKB

cycles when

reading,

2 or 3 PCLKB

cycles when

writing

3 ICLK cycles

when reading,

2 ICLK cycles

when writing

section 40.

0008 AC3Ch SDHI SD Status Register 2 SDSTS2 32 32 3 or 4 PCLKB

cycles when

reading,

2 or 3 PCLKB

cycles when

writing

3 ICLK cycles

when reading,

2 ICLK cycles

when writing

section 40.

0008 AC40h SDHI SD Interrupt Mask Register 1 SDIMSK1 32 32 3 or 4 PCLKB

cycles when

reading,

2 or 3 PCLKB

cycles when

writing

3 ICLK cycles

when reading,

2 ICLK cycles

when writing

section 40.

0008 AC44h SDHI SD Interrupt Mask Register 2 SDIMSK2 32 32 3 or 4 PCLKB

cycles when

reading,

2 or 3 PCLKB

cycles when

writing

3 ICLK cycles

when reading,

2 ICLK cycles

when writing

section 40.

0008 AC48h SDHI SDHI Clock Control Register SDCLKCR 32 32 3 or 4 PCLKB

cycles when

reading,

2 or 3 PCLKB

cycles when

writing

3 ICLK cycles

when reading,

2 ICLK cycles

when writing

section 40.

0008 AC4Ch SDHI Transfer Data Size Register SDSIZE 32 32 3 or 4 PCLKB

cycles when

reading,

2 or 3 PCLKB

cycles when

writing

3 ICLK cycles

when reading,

2 ICLK cycles

when writing

section 40.

000

8 AC50h SDHI Card Access Option Register SDOPT 32 32 3 or 4 PCLKB

cycles when

reading,

2 or 3 PCLKB

cycles when

writing

3 ICLK cycles

when reading,

2 ICLK cycles

when writing

section 40.

0008 AC58h SDHI SD Error Status Register 1 SDERSTS1 32 32 3 or 4 PCLKB

cycles when

reading,

2 or 3 PCLKB

cycles when

writing

3 ICLK cycles

when reading,

2 ICLK cycles

when writing

section 40.

0008 AC5Ch SDHI SD Error Status Register 2 SDERSTS2 32 32 3 or 4 PCLKB

cycles when

reading,

2 or 3 PCLKB

cycles when

writing

3 ICLK cycles

when reading,

2 ICLK cycles

when writing

section 40.

0008 AC60h SDHI SD Buffer Register SDBUFR 32 32 3 or 4 PCLKB

cycles when

reading,

2 or 3 PCLKB

cycles when

writing

3 ICLK cycles

when reading,

2 ICLK cycles

when writing

section 40.

Table 5.1 List of I/O Registers (Address Order) (11/31)

Address

Module

Symbol Register Name

Register

Symbol

Number

of Bits

Access

Size

Number of Access Cycles

Reference

SectionICLK PCLK ICLK <PCLK

Loading...

Loading...