R01UH0823EJ0100 Rev.1.00 Page 977 of 1823

Jul 31, 2019

RX23W Group 33. Serial Communications Interface (SCIg, SCIh)

33.2.8 Serial Control Register (SCR)

Note: Some bits in the SCR register have different functions in smart card interface mode and non-smart card interface

mode.

(1) Non-Smart Card Interface Mode (SCMR.SMIF = 0)

x: Don’t care

Note 1. Writable only when TE = 0 and RE = 0.

Note 2. TMR clock is selectable for SCI5 and SCI12.

Note 3. 1 can be written only when TE = 0 and RE = 0, while the SMR.CM bit is 1. After setting TE or RE to 1, only 0 can be written to

TE and RE. While the SMR.CM bit is 0 and the SIMR1.IICM bit is 0, writing is enabled under any condition.

Address(es): SCI1.SCR 0008 A022h, SCI5.SCR 0008 A0A2h, SCI8.SCR 0008 A102h, SCI12.SCR 0008 B302h

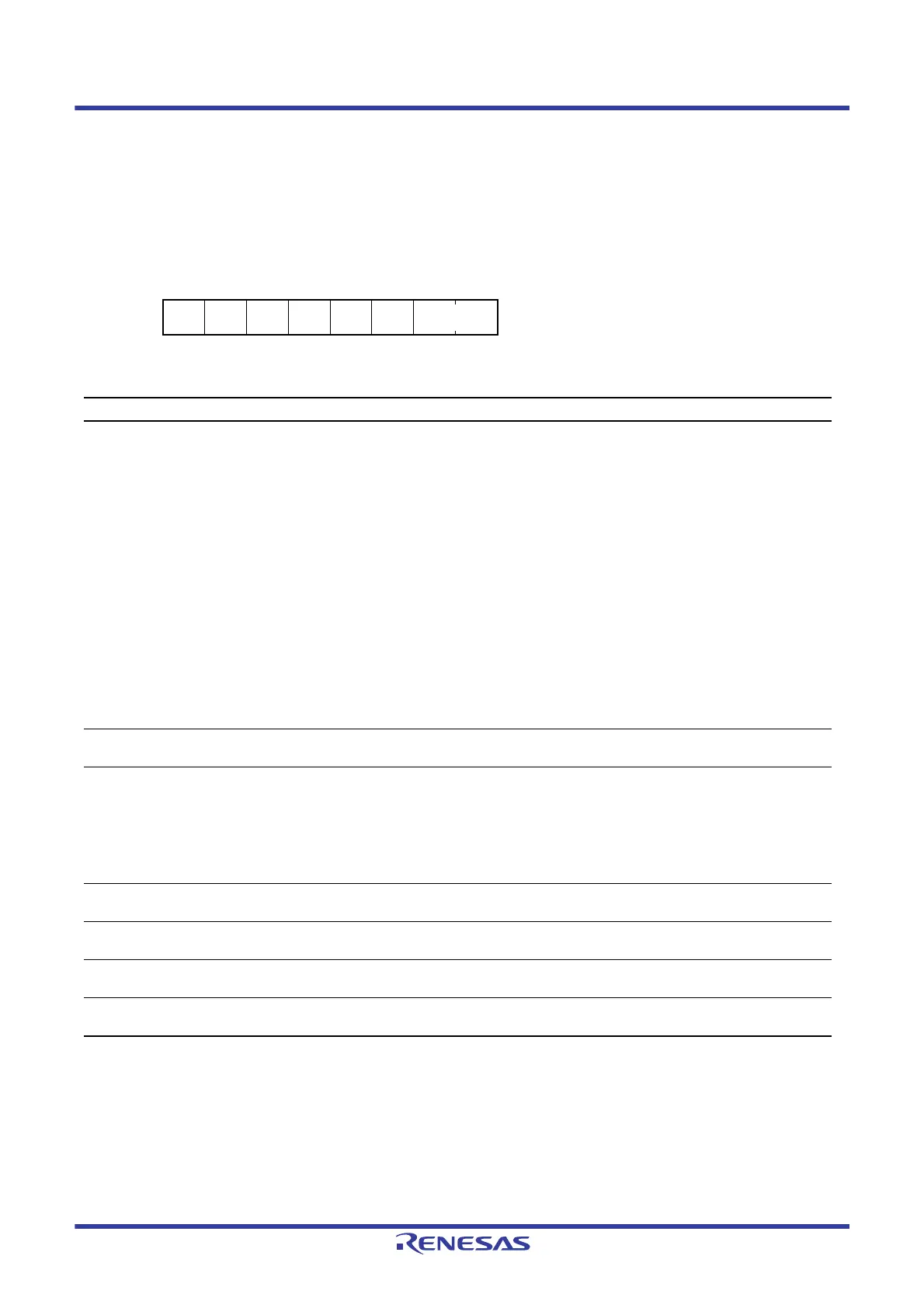

b7 b6 b5 b4 b3 b2 b1 b0

TIE RIE TE RE MPIE TEIE CKE[1:0]

Value after reset:

00000000

Bit Symbol Bit Name Description R/W

b1, b0 CKE[1:0] Clock Enable (Asynchronous mode)

b1 b0

0 0: On-chip baud rate generator

The SCKn pin becomes high-impedance.

0 1: On-chip baud rate generator

The clock with the same frequency as the bit rate is output

from the SCKn pin.

1 x: External clock or TMR clock*

2

• The clock with a frequency 16 times the bit rate should be

input from the SCKn pin. Input a clock signal with a frequency

eight times the bit rate when the SEMR.ABCS bit is 1.

• The SCKn pin becomes high-impedance when the TMR

clock*

2

is used.

(Clock synchronous mode)

b1 b0

0 x: Internal clock

The SCKn pin functions as the clock output pin.

1 x: External clock

The SCKn pin functions as the clock input pin.

R/W*

1

b2 TEIE Transmit End Interrupt Enable 0: A TEI interrupt request is disabled

1: A TEI interrupt request is enabled

R/W

b3 MPIE Multi-Processor Interrupt

Enable

(Valid in asynchronous mode when SMR.MP = 1)

0: Normal reception

1: When the data with the multi-processor bit set to 0 is received,

the data is not read, and setting the status flags ORER and FER

in SSR to 1 is disabled. When the data with the multi-processor

bit set to 1 is received, the MPIE bit is automatically cleared to 0,

and normal reception is resumed.

R/W

b4 RE Receive Enable 0: Serial reception is disabled

1: Serial reception is enabled

R/W*

3

b5 TE Transmit Enable 0: Serial transmission is disabled

1: Serial transmission is enabled

R/W*

3

b6 RIE Receive Interrupt Enable 0: RXI and ERI interrupt requests are disabled

1: RXI and ERI interrupt requests are enabled

R/W

b7 TIE Transmit Interrupt Enable 0: A TXI interrupt request is disabled

1: A TXI interrupt request is enabled

R/W

Loading...

Loading...