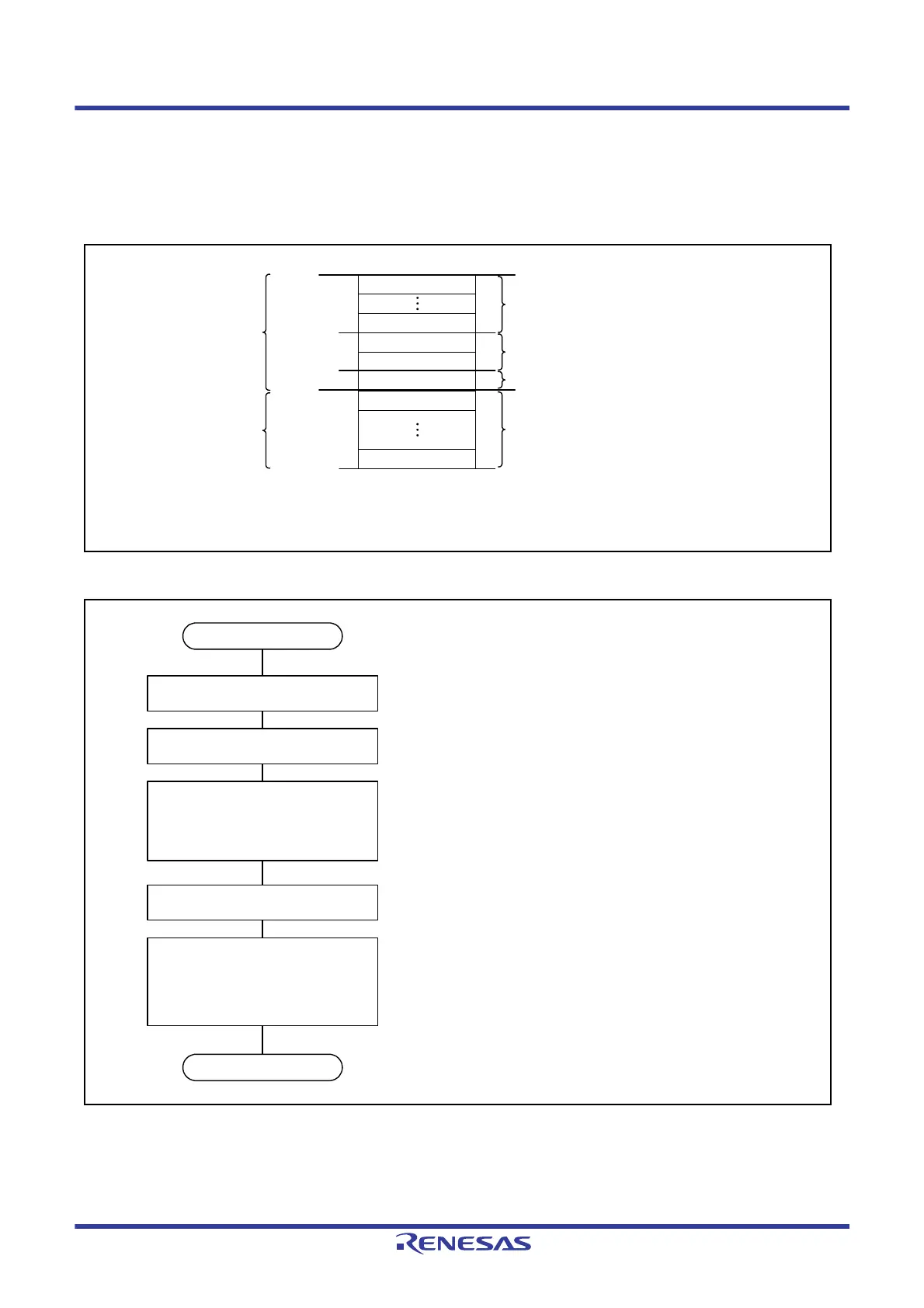

buffers to be linked.

Receive buffer 0

Receive buffer n

Receive FIFO 0

Receive FIFO 1

Transmit/receive FIFO 0

Transmit buffer 0

Transmit buffer 3

Receive buffers

Receive FIFO buffers

Transmit/receive FIFO buffer

Transmit buffers

Maximum 16 buffers

4 buffers fixed

Note: Receive buffers, receive FIFO buffers, transmit/receive FIFO buffer, and transmit buffers are located in succession.

• Select interrupt request timing by the RFIGCV[2:0] bits.

• Select an interrupt source by the RFIM bit.

• Set the FIFO buffer depth by the RFDC[2:0] bits.

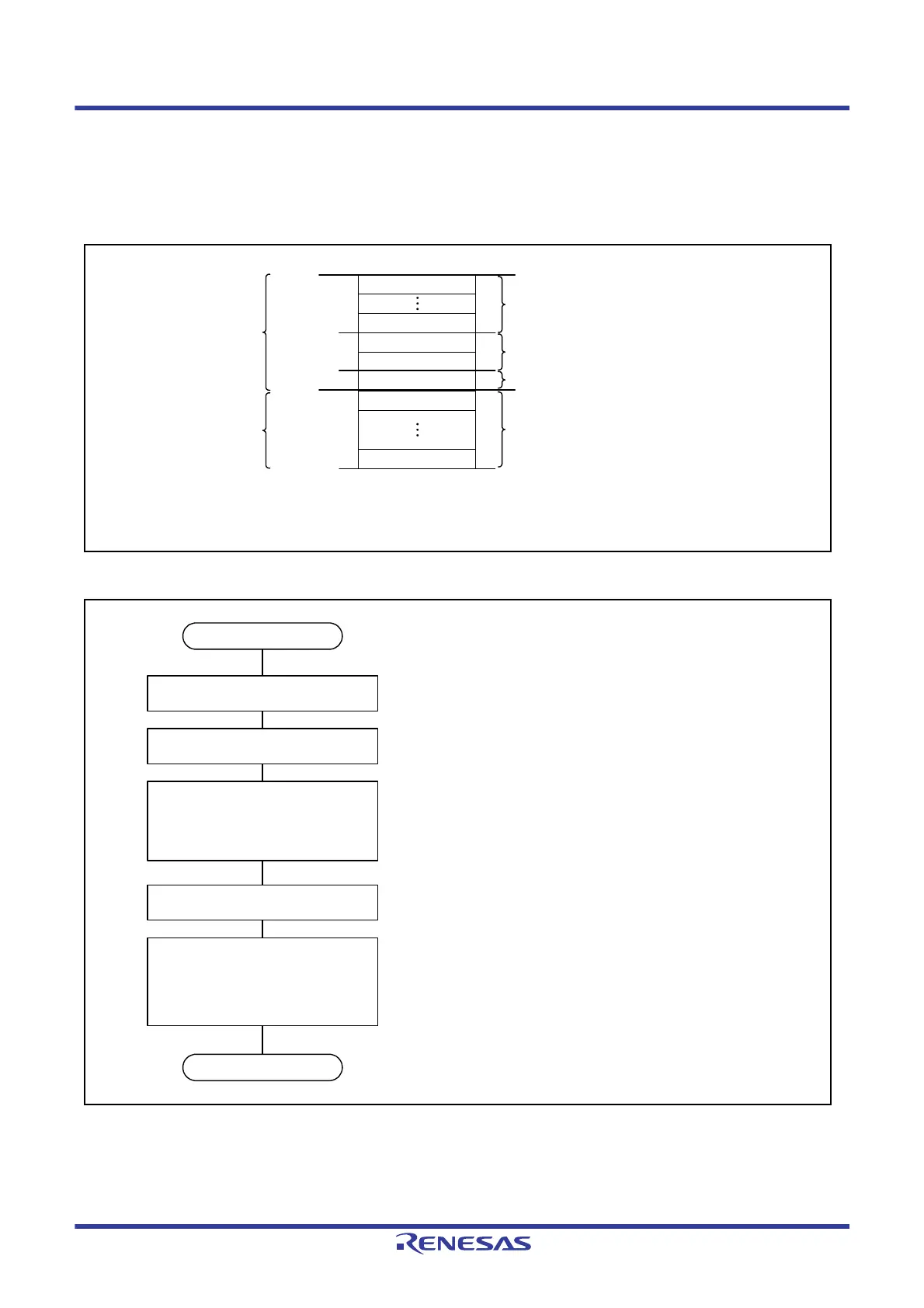

Start

End

Set transmit history buffer

(the THLCC0 register)

Set receive buffer (the RMNB register)

Set receive FIFO buffer

(the RFCCm register)

Set transmit/receive FIFO buffer

(the CFCCH0 and CFCCL0 registers)

• Set the number of transmit buffer to be linked by the CFTML[1:0] bits.

• Select an interval timer count source by the CFITR and CFITSS bits.

• Select a mode by the CFM[1:0] bits.

• Select receive interrupt request timing by the CFIGCV[2:0] bits.

• Select an interrupt source by the CFIM bit.

• Set the FIFO buffer depth by the CFDC[2:0] bits.

• Select a message transmit source buffer type by the TH LDTE bit.

• Select an interrupt source by the THLIM bit.

Enable interrupt of buffer to be used

• Enable receive FIFO interrupts by the RFCCm.RFIE bit.

• Enable transmit/receive FIFO transmit interrupts by the CFCCL0.CFTXIE bit.

• Enable transmit/receive FIFO receive interrupts by the CFCCL0.CFRXIE bit.

• Enable transmit abort interrupts by the CTRH.TAIE bit.

• Enable transmit complete interrupts by the TMIEC.TMIEp bit.

• Enable transmit history interrupts by the THLCC0.THLIE bit.

• Set the number of receive buffers (0 to 16) by the NRXMB[4:0] bits.

Loading...

Loading...