R01UH0823EJ0100 Rev.1.00 Page 1289 of 1823

Jul 31, 2019

RX23W Group 36. CAN Module (RSCAN)

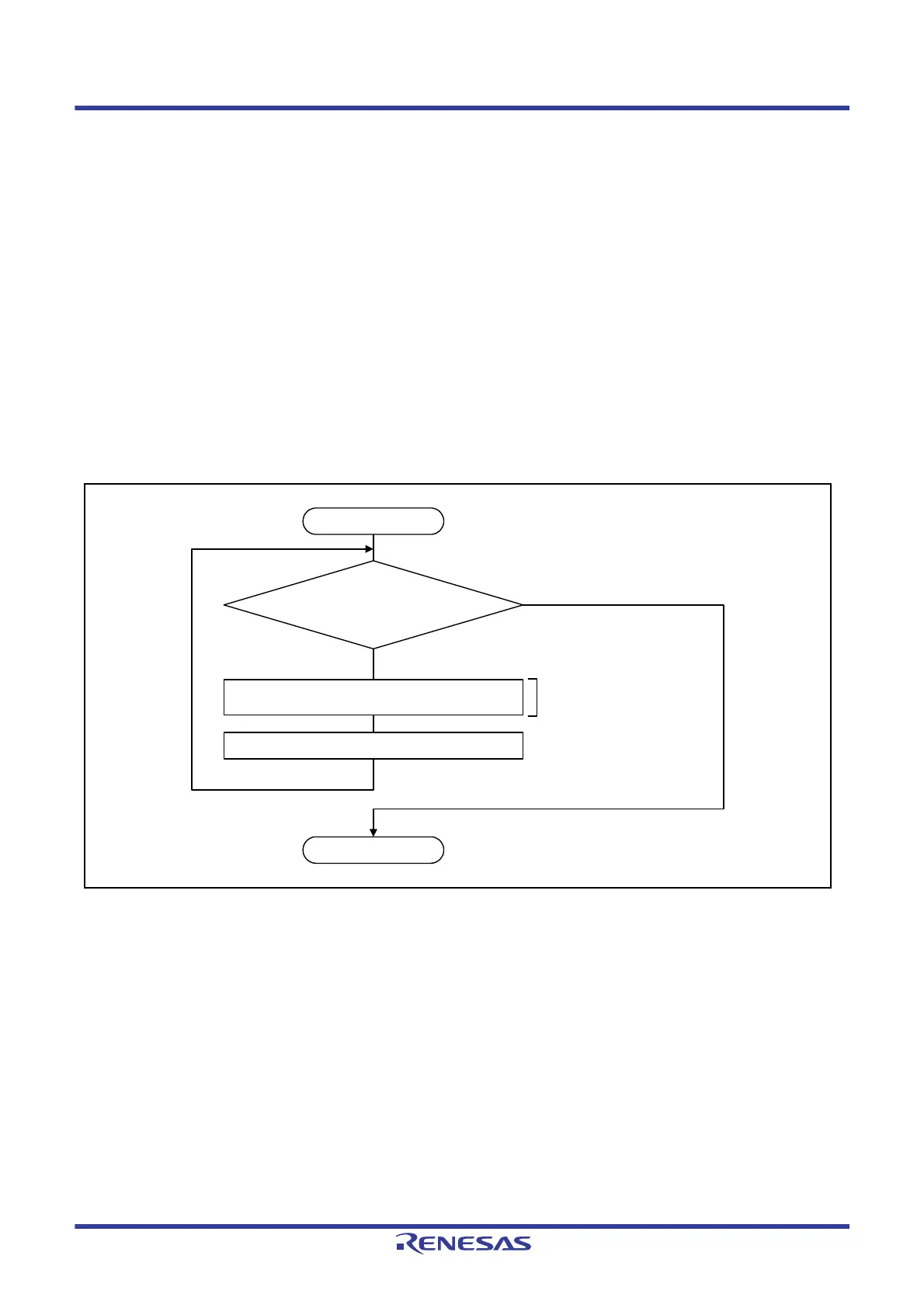

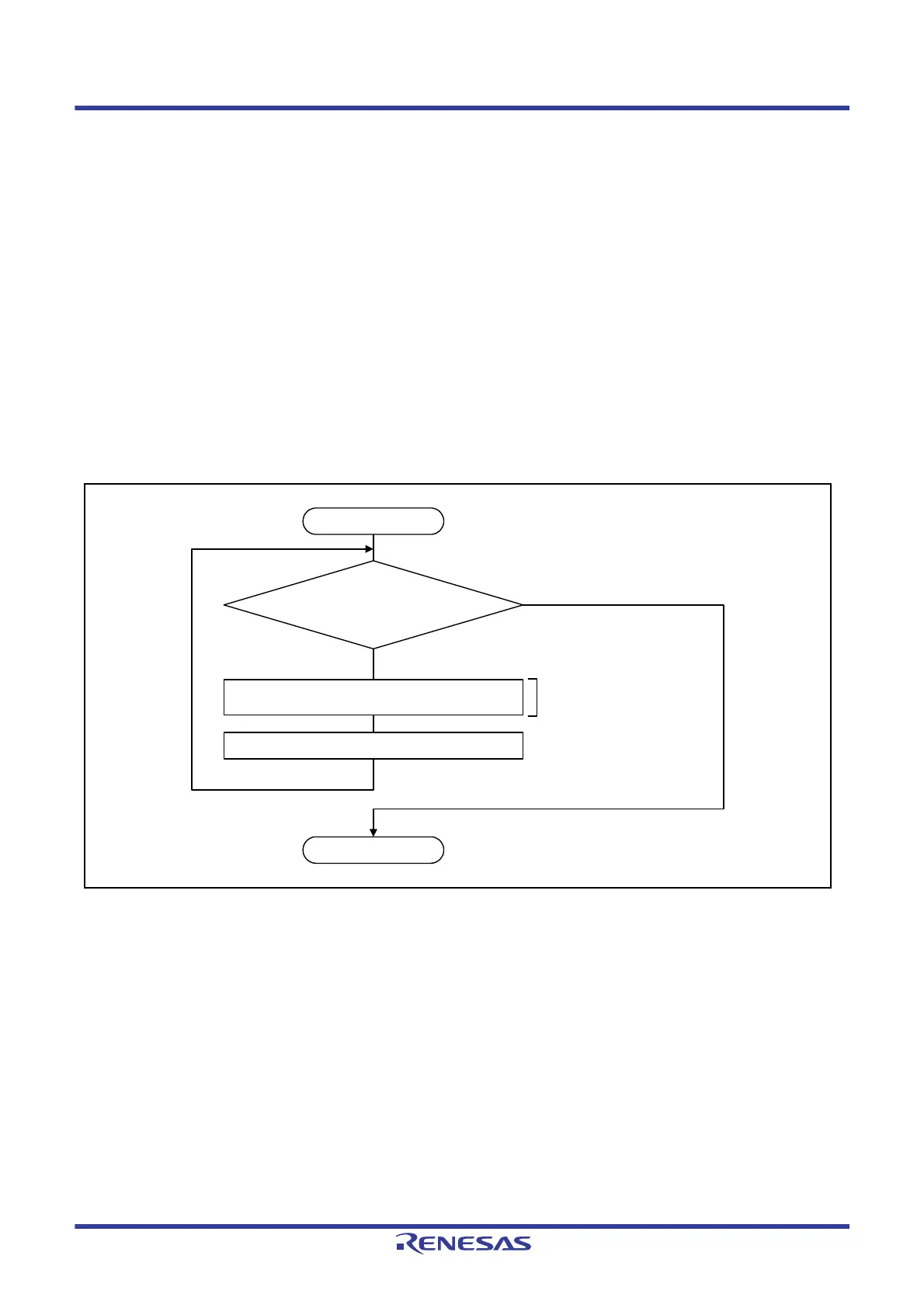

36.10.2 FIFO Buffer Reading Procedure

When received messages have been stored in one or more receive FIFO buffers or a transmit/receive FIFO buffer that is

set to receive mode, the corresponding message count display counter (RFSTSm.RFMC[5:0] flags or

CFSTS0.CFMC[5:0] flags) is incremented. At this time, when the RFCCm.RFIE bit (receive FIFO interrupt is enabled)

or the CFCCL0.CFRXIE bit (transmit/receive FIFO receive interrupt is enabled) is set to 1, an interrupt request is

generated. Received messages can be read from the RFIDLm, RFIDHm, RFTSm, RFPTRm, and RFDF0m to RFDF3m

registers (receive FIFO buffers) or the CFIDL0, CFIDH0, CFTS0, CFPTR0, and CFDF00 to CFDF30 registers (transmit/

receive FIFO buffers). Messages in FIFO buffers can be read sequentially on a first-in, first-out basis.

When the message count display counter value matches the FIFO buffer depth (a value set by the RFCCm.RFDC[2:0]

bits or the CFCCL0.CFDC[2:0] bits), the RFFLL or CFFLL flag becomes 1 (the receive FIFO buffer is full).

When all messages have been read out of the FIFO buffer, the RFSTSm.RFEMP flag or CFSTS0.CFEMP flag becomes

1 (the receive FIFO buffer contains no unread message (buffer empty)).

If the RFCCm.RFE bit or the CFCCL0.CFE bit is set to 0 (no receive FIFO buffer is used) with the interrupt request flag

(RFSTSm.RFIF flag or CFSTS0.CFRXIF flag) set to 1 (a receive FIFO interrupt request is present), the interrupt request

flag is not automatically set to 0. Set the interrupt request flag to 0 by the program.

Figure 36.24 Transmit/Receive FIFO Buffer Reading Procedure

Start

End

Is transmit/receive FIFO buffer empty?

(Is the CFSTS0.CFEMP bit 1?)

No

Yes

Set the CFPCTR0 register to FFh.

Read messages from registers CFIDL0, CFIDH0, CFTS0,

CFPTR0, and CFDF00 to CFDF30.

Read messages when the

GRWCR.RPAGE bit is set to 1.

Loading...

Loading...