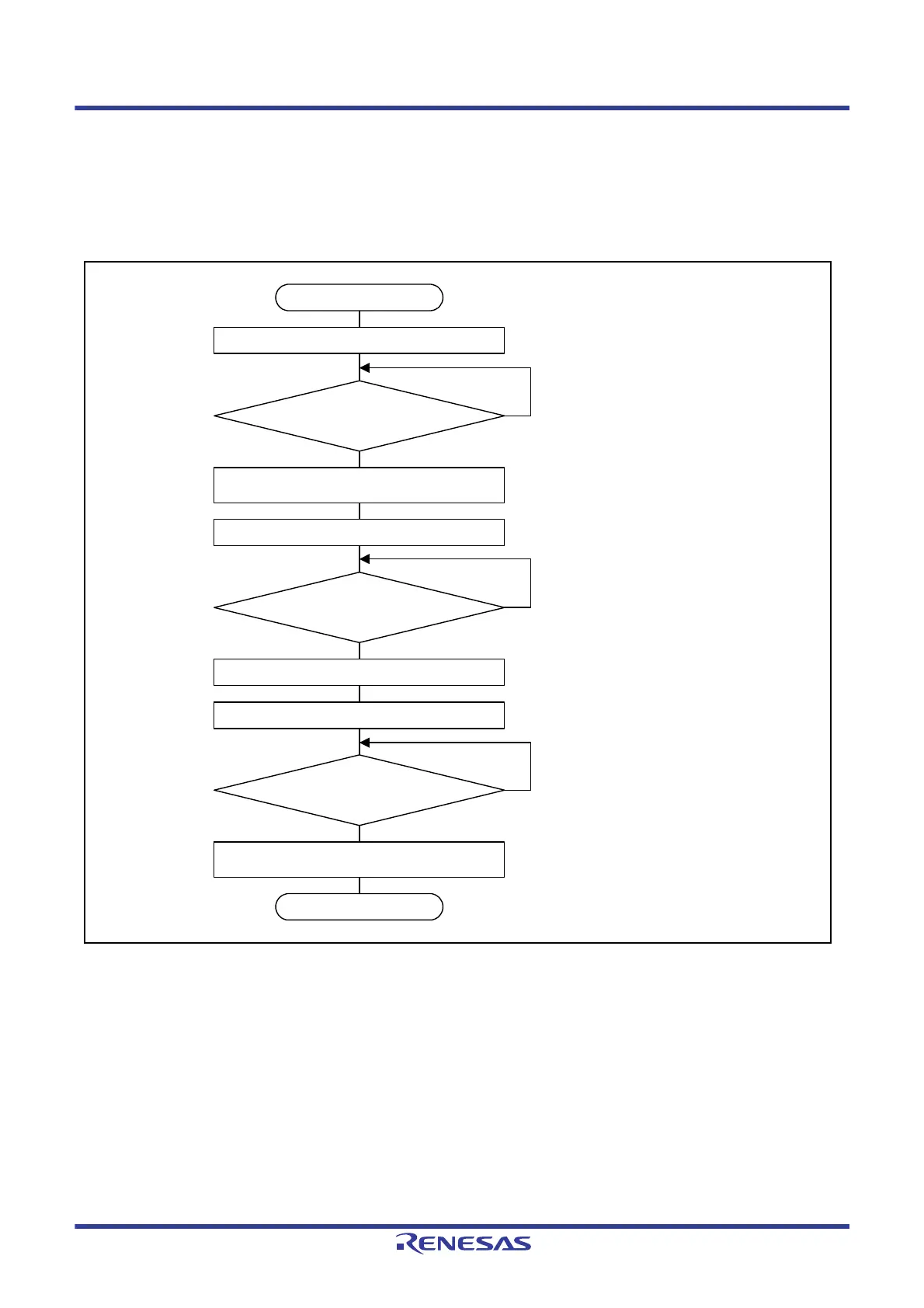

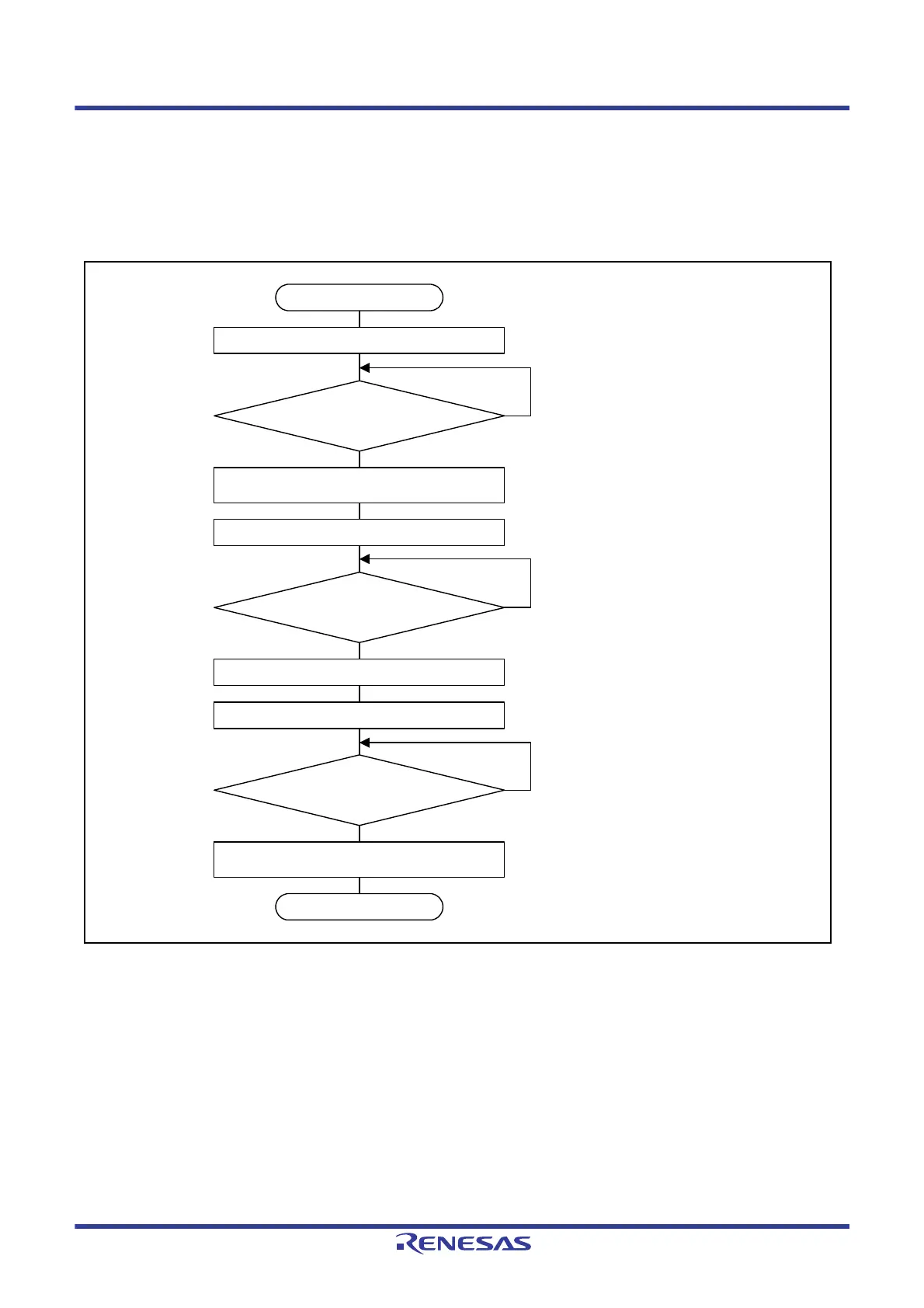

Yes

No

Is the STSL.CHLTSTS flag 1

(in channel halt mode)?

Channel halt mode

Start

End

Set the CTRL.CHMDC[1:0] bit to 10b.

Set the CTRH.CTME bit to 1.

Set the CTMS[1:0] bits to 10b or 11b.

Set the CTRL.CHMDC[1:0] bits to 00b.

Are all STSL.CSLPSTS, CHLTSTS, and

CRSTSTS flags 0?

Perform self-test in channel 0.

Set the CTRL.CHMDC[1:0] to 10b.

Is the STSL.CHLTSTS flag 1

(channel halt mode)?

Set the CTRH.CTME bit to 0.

Set the CTMS[1:0] bits to 00b.

Communication test mode is enabled.

Self-test mode 0 (10b) or 1 (11b).

Channel communication mode

Channel halt mode

Communication test mode is disabled.

Standard test mode

Yes

No

Yes

No

Loading...

Loading...