R01UH0823EJ0100 Rev.1.00 Page 743 of 1823

Jul 31, 2019

RX23W Group 26. 8-Bit Timer (TMR)

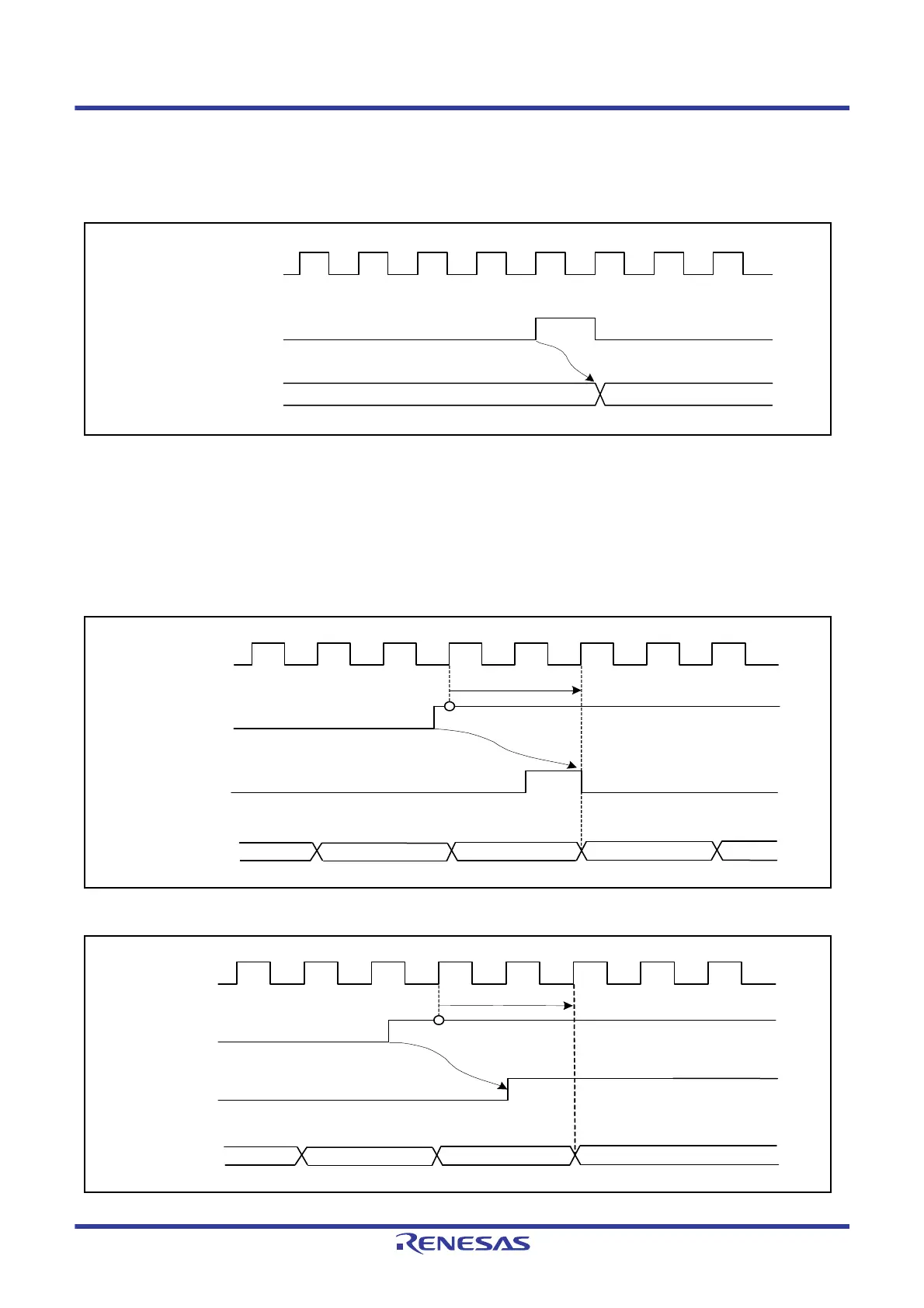

26.4.4 Timing of Counter Clear by Compare Match

TCNT is cleared when compare match A or B occurs, depending on the settings of the TCR.CCLR[1:0] bits.

Figure 26.9 shows the timing of this operation.

Figure 26.9 Timing of Counter Clear by Compare Match

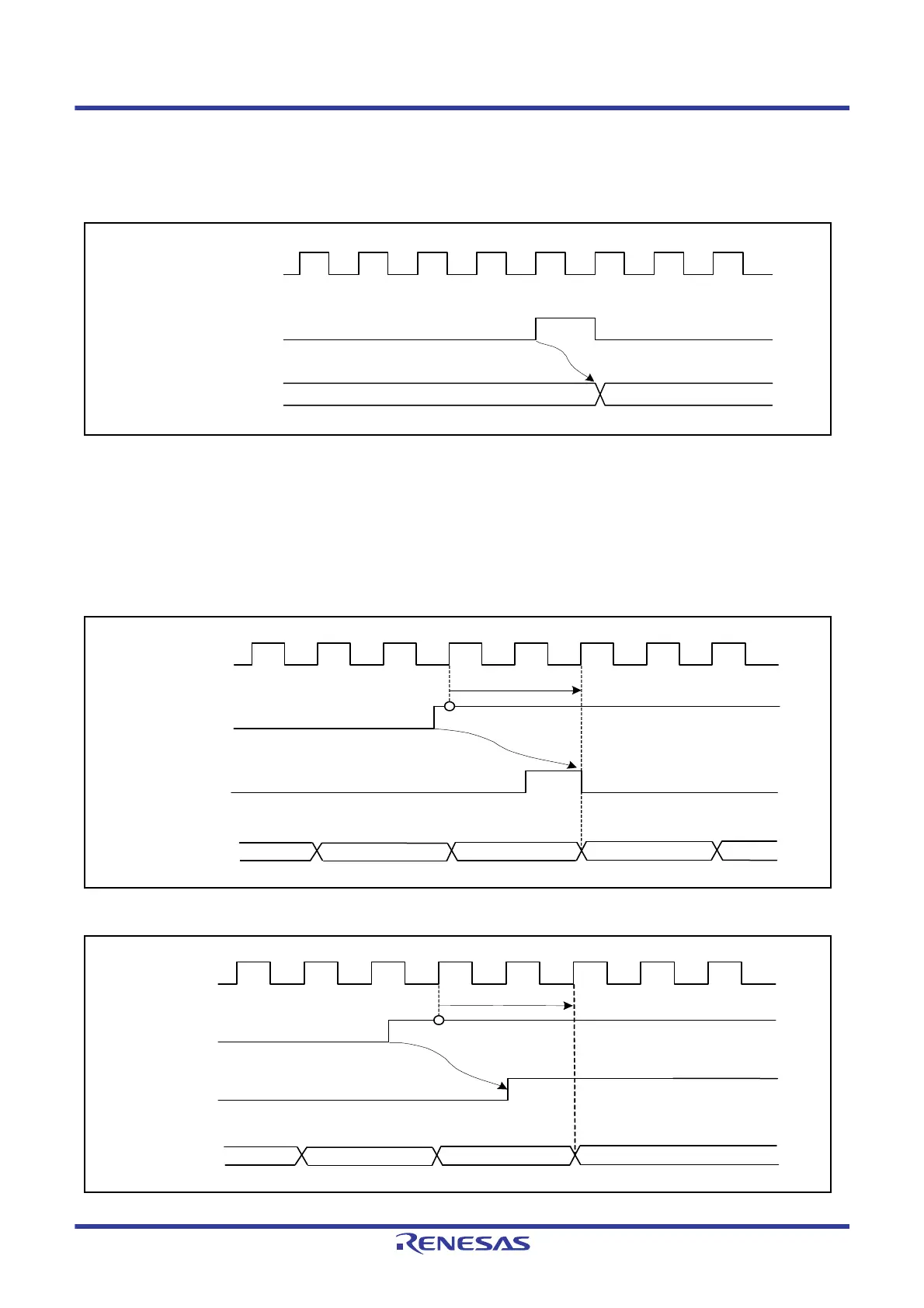

26.4.5 Timing of the External Reset for TCNT

TCNT is cleared at the rising edge or high level of an external counter reset signal, depending on the settings of the

TCR.CCLR[1:0] bits. At least 2 PCLK cycles are required from a reset input to clearing of TCNT.

Figure 26.10 and Figure 26.11 show the timing of this operation.

Figure 26.10 Clear Timing by External Counter Reset Signal (Rising Edge)

Figure 26.11 Clear Timing by External Counter Reset Signal (High Level)

Compare match signal

TCNT

PCLK

N00h

TMRIn pin

Clear signal

TCNT

PCLK

2 PCLK

N – 2

N – 1 N

00h

01h

TMRIn pin

Clear signal

PCLK

2 PCLK

TCNT

N – 2 N – 1 N

00h

Loading...

Loading...