R01UH0823EJ0100 Rev.1.00 Page 1358 of 1823

Jul 31, 2019

RX23W Group 38. Serial Peripheral Interface (RSPIa)

38.3 Operation

In this section, the serial transfer period means a period from the beginning of driving valid data to the fetching of the

final valid data.

38.3.1 Overview of RSPI Operations

The RSPI is capable of synchronous serial transfers in slave mode (SPI operation), single-master mode (SPI operation),

multi-master mode (SPI operation), slave mode (clock synchronous operation), and master mode (clock synchronous

operation). A particular mode of the RSPI can be selected by using the MSTR, MODFEN, and SPMS bits in SPCR.

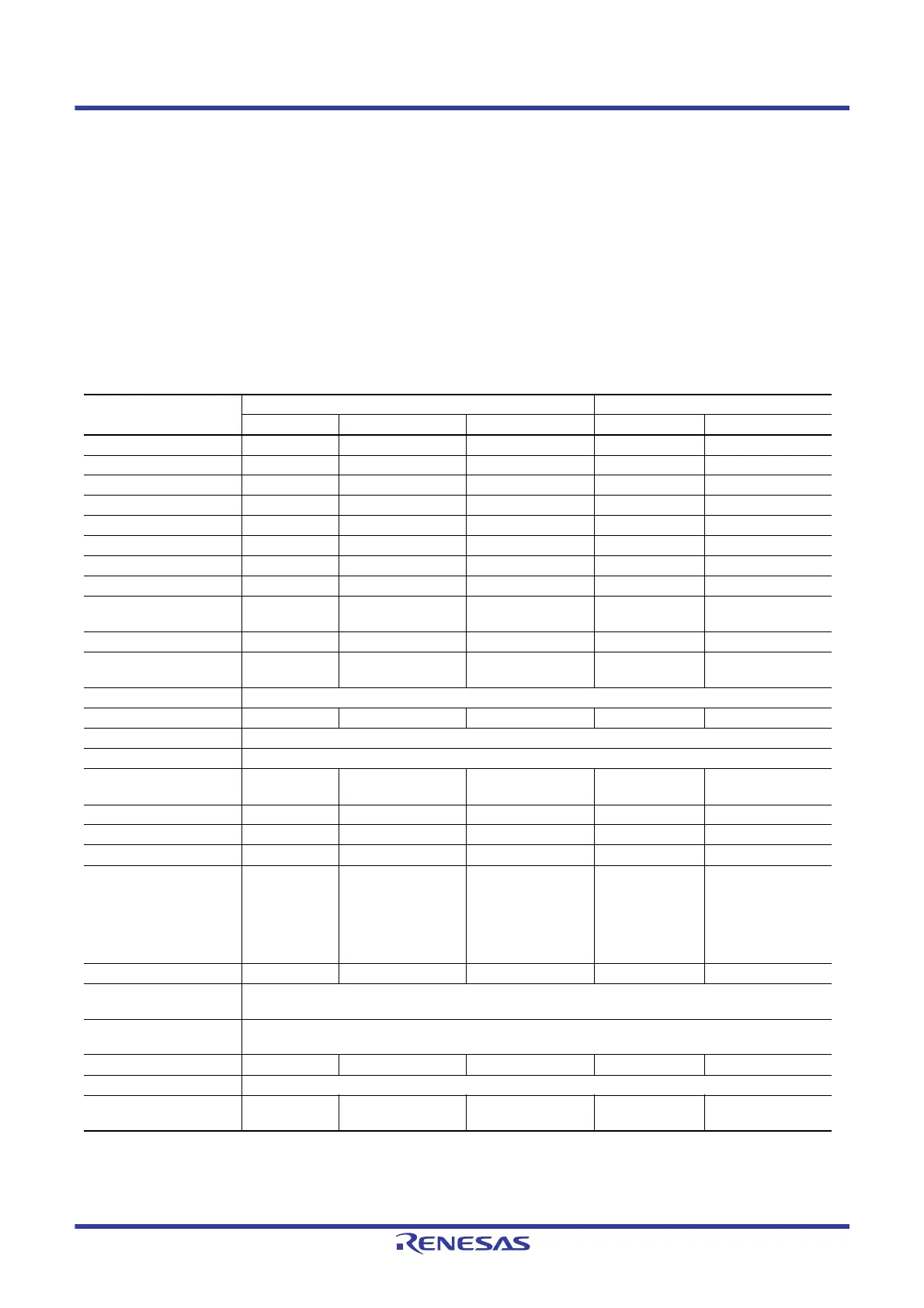

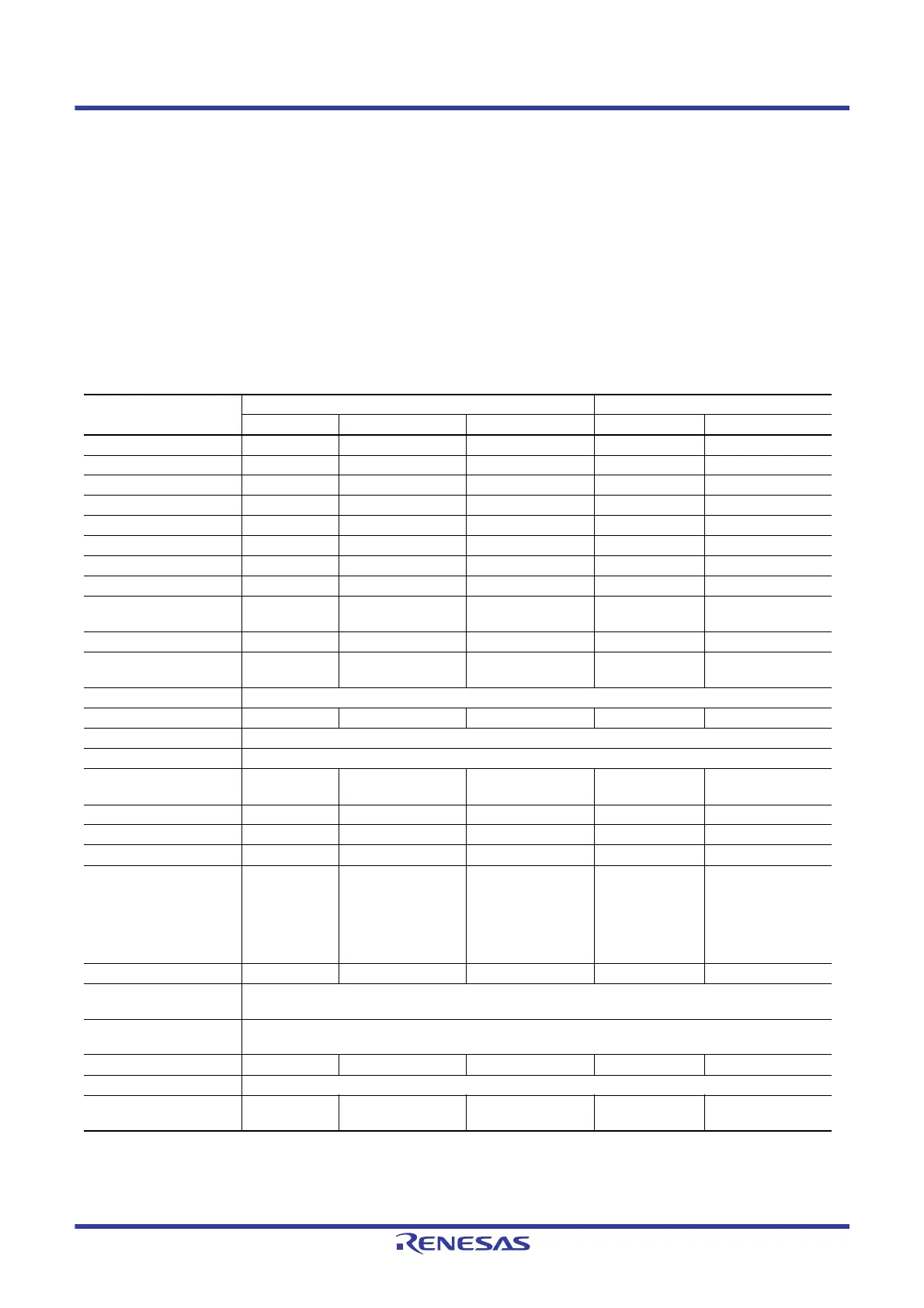

Table 38.5 lists the relationship between RSPI modes and SPCR settings, and a description of each mode.

Note 1. This function is not supported in this mode.

Note 2. When the SPCR.TXMD bit is 1, receiver buffer full detection, overrun error detection, and parity error detection are not performed.

Note 3. When the SPCR2.SPPE bit is 0, parity error detection is not performed.

Note 4. When the SPCR2.SCKASE bit is 1, overrun error detection does not proceed.

Table 38.5 Relationship between RSPI Modes and SPCR Settings and Description of Each Mode

Mode

SPI Operation Clock Synchronous Operation

Slave Single-Master Multi-Master Slave Master

MSTR bit setting 0 1 1 0 1

MODFEN bit setting 0 or 1 0 1 0 0

SPMS bit setting 0 0 0 1 1

RSPCKA signal Input Output Output/Hi-Z Input Output

MOSIA signal Input Output Output/Hi-Z Input Output

MISOA signal Output/Hi-Z Input Input Output Input

SSLA0 signal Input Output Input Hi-Z*

1

Hi-Z*

1

SSLA1, SSLA3 signals Hi-Z*

1

Output Output/Hi-Z Hi-Z*

1

Hi-Z*

1

SSL polarity change

function

Supported Supported Supported — —

Transfer rate Up to PCLK/8 Up to PCLK/2 Up to PCLK/2 Up to PCLK/8 Up to PCLK/2

Clock source RSPCK input On-chip baud rate

generator

On-chip baud rate

generator

RSPCK input On-chip baud rate

generator

Clock polarity Two

Clock phase Two Two Two One (CPHA = 1) Two

First transfer bit MSB/LSB

Transfer data length 8 to 16, 20, 24, 32 bits

Burst transfer Possible

(CPHA = 1)

Possible

(CPHA = 0,1)

Possible

(CPHA = 0,1)

——

RSPCK delay control Not supported Supported Supported Not supported Supported

SSL negation delay control Not supported Supported Supported Not supported Supported

Next-access delay control Not supported Supported Supported Not supported Supported

Transfer activation method SSL input active

or RSPCK

oscillation

Transmit buffer is

written to when a

transmit buffer empty

interrupt request is

generated or the

SPTEF flag is 1

Transmit buffer is

written to when a

transmit buffer empty

interrupt request is

generated or the

SPTEF flag is 1

RSPCK oscillation Transmit buffer is

written to when a

transmit buffer empty

interrupt request is

generated or the

SPTEF flag is 1

Sequence control Not supported Supported Supported Not supported Supported

Transmit buffer empty

detection

Supported

Receive buffer full

detection

Supported*

2

Overrun error detection Supported*

2

Supported*

2,

*

4

Supported*

2,

*

4

Supported*

2

Supported*

2

Parity error detection Supported*

2,

*

3

Mode fault error detection Supported

(MODFEN = 1)

Not supported Supported Not supported Not supported

Loading...

Loading...