R01UH0823EJ0100 Rev.1.00 Page 213 of 1823

Jul 31, 2019

RX23W Group 10. Clock Frequency Accuracy Measurement Circuit (CAC)

10.2.2 CAC Control Register 1 (CACR1)

Note: Set the CACR1 register when the CACR0.CFME bit is 0.

CACREFE Bit (CACREF Pin Input Enable)

This bit specifies whether the CACREF pin input is enabled or disabled.

FMCS[2:0]Bits (Measurement Target Clock Select)

These bits select the measurement target clock whose frequency is to be measured.

TCSS[1:0] Bits (Timer Count Clock Source Select)

These bits select the count clock source for the clock frequency accuracy measurement circuit.

EDGES[1:0]Bits (Valid Edge Select)

These bits select the valid edge for the reference signal.

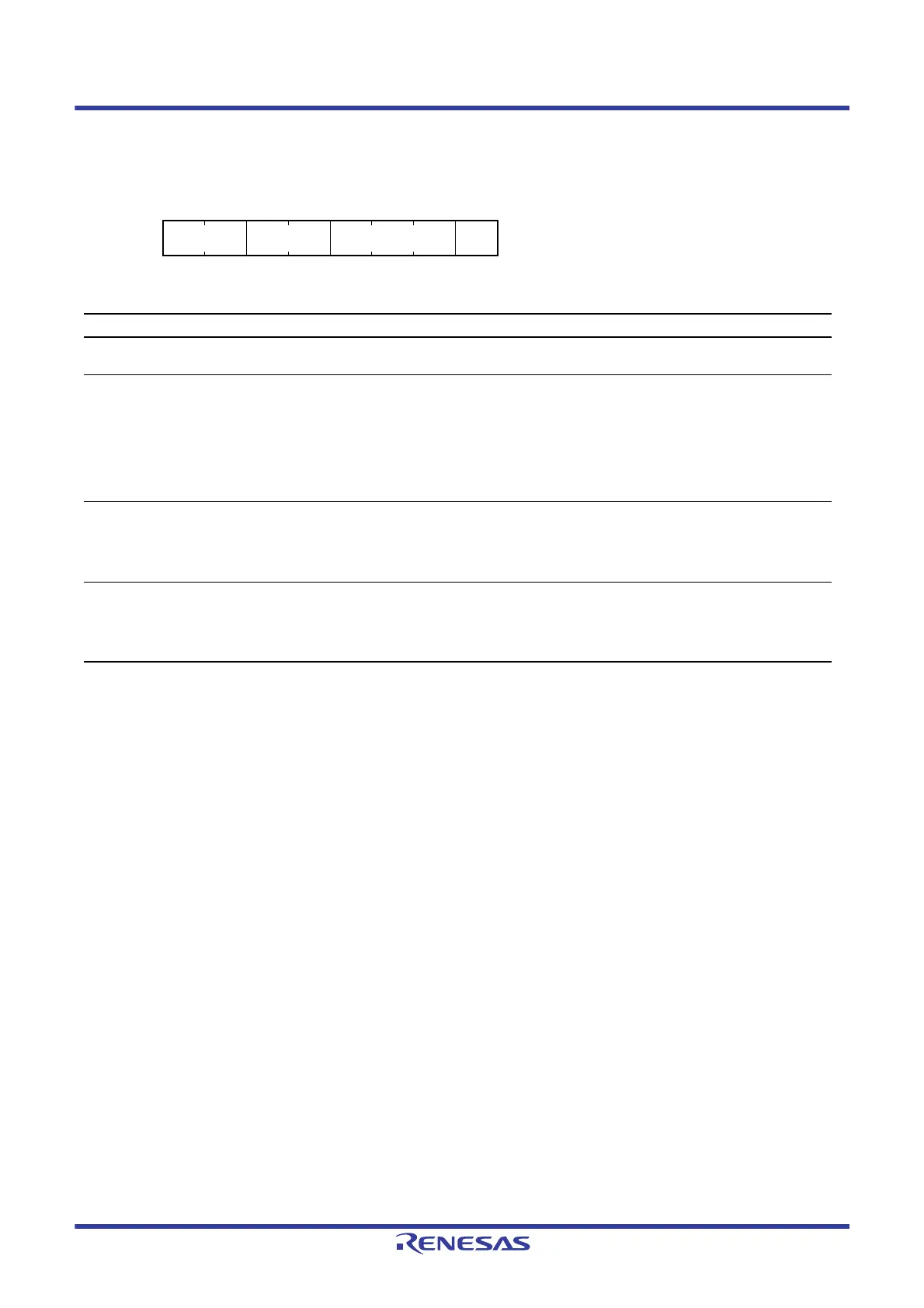

Address(es): 0008 B001h

b7 b6 b5 b4 b3 b2 b1 b0

EDGES[1:0] TCSS[1:0] FMCS[2:0]

CACRE

FE

Value after reset:

00000000

Bit Symbol Bit Name Description R/W

b0 CACREFE CACREF Pin Input Enable 0: CACREF pin input is disabled.

1: CACREF pin input is enabled.

R/W

b3 to b1 FMCS[2:0] Measurement Target Clock Select

b3 b1

0 0 0: Main clock

0 0 1: Sub-clock

0 1 0: HOCO clock

0 1 1: LOCO clock

1 0 0: IWDT-dedicated clock (IWDTCLK)

1 0 1: Peripheral module clock B (PCLKB)

Settings other than above are prohibited.

R/W

b5, b4 TCSS[1:0] Timer Count Clock Source Select

b5 b4

0 0: No division

0 1: ×1/4 clock

1 0: ×1/8 clock

1 1: ×1/32 clock

R/W

b7, b6 EDGES[1:0] Valid Edge Select

b7 b6

0 0: Rising edge

0 1: Falling edge

1 0: Both rising and falling edges

1 1: Setting prohibited

R/W

Loading...

Loading...