R01UH0823EJ0100 Rev.1.00 Page 394 of 1823

Jul 31, 2019

RX23W Group 19. Data Transfer Controller (DTCa)

19.4.2 Transfer Information Write-Back Skip Function

When the MRA.SM[1:0] bits or the MRB.DM[1:0] bits are set to “address is fixed” (00b or 01b), a part of transfer

information is not written back. This function is performed independently of the setting of short-address mode or full-

address mode.

Table 19.4 lists transfer information write-back skip conditions and applicable registers. The CRA and CRB registers

are written back independently of the setting of short-address mode or full-address mode.

Furthermore, in full-address mode, write-back of registers MRA and MRB is skipped.

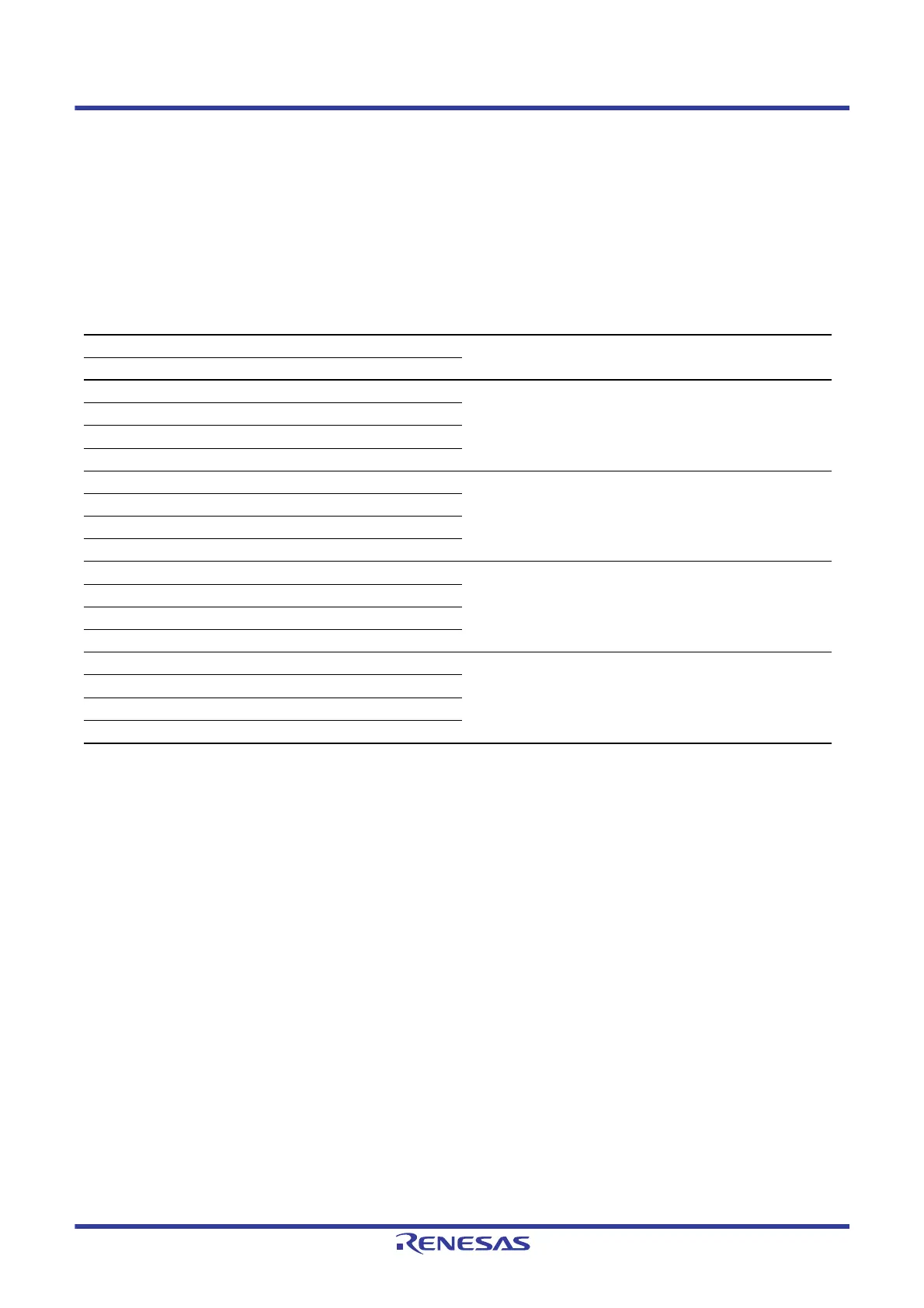

Table 19.4 Transfer Information Write-Back Skip Conditions and Applicable Registers

MRA.SM[1:0] Bits MRB.DM[1:0] Bits

SAR Register DAR Register

b3 b2 b3 b2

0000Skip Skip

0001

0100

0101

0010Skip Write-back

0011

0110

0111

1000Write-back Skip

1001

1100

1101

1010Write-back Write-back

1011

1110

1111

Loading...

Loading...