R01UH0823EJ0100 Rev.1.00 Page 643 of 1823

Jul 31, 2019

RX23W Group 24. Port Output Enable 2 (POE2a)

24.2 Register Descriptions

24.2.1 Input Level Control/Status Register 1 (ICSR1)

Note 1. Can be modified only once after a reset.

Note 2. Writing 0 to this bit after reading it as 1 clears the flag and is the only allowed way.

Address(es): 0008 8900h

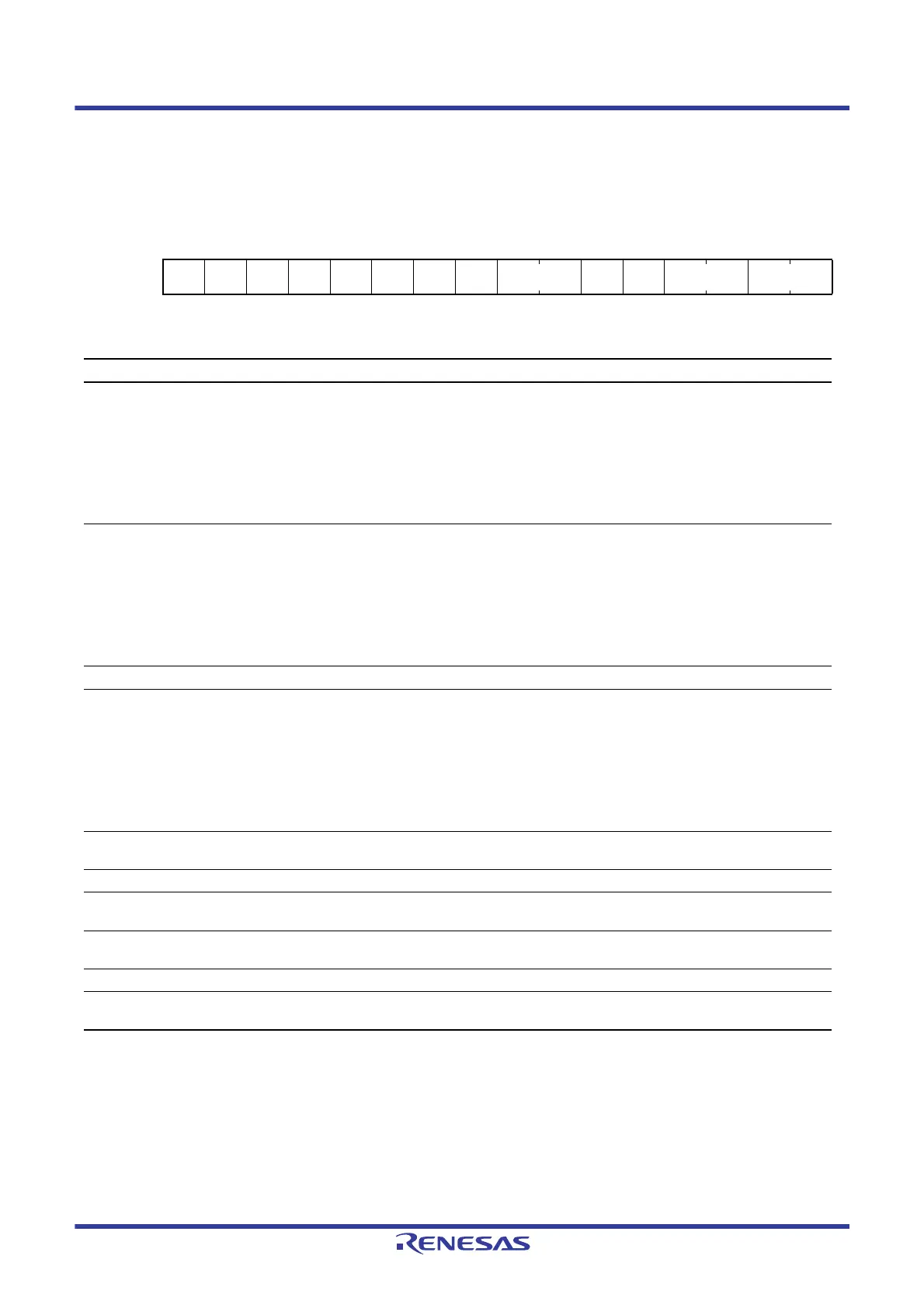

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

POE3F — POE1F POE0F — — — PIE1 POE3M[1:0] — — POE1M[1:0] POE0M[1:0]

Value after reset:

0000000000000000

Bit Symbol Bit Name Description R/W

b1, b0 POE0M[1:0] POE0 Mode

Select

b1 b0

0 0: Accepts a high-impedance request on the falling edge of the POE0# pin

input.

0 1: Accepts a high-impedance request when the POE0# pin input has been

sampled 16 times at PCLK/8 clock cycles and all are low level.

1 0: Accepts a high-impedance request when POE0# input has been sampled 16

times at PCLK/16 clock pulses and all are low level.

1 1: Accepts a high-impedance request when POE0# input has been sampled 16

times at PCLK/128 clock pulses and all are low level.

R/W*

1

b3, b2 POE1M[1:0] POE1 Mode

Select

b3 b2

0 0: Accepts a high-impedance request on the falling edge of the POE1# pin

input.

0 1: Accepts a high-impedance request when the POE1# pin input has been

sampled 16 times at PCLK/8 clock cycles and all are low level.

1 0: Accepts a high-impedance request when POE1# input has been sampled 16

times at PCLK/16 clock pulses and all are low level.

1 1: Accepts a high-impedance request when POE1# input has been sampled 16

times at PCLK/128 clock pulses and all are low level.

R/W*

1

b5, b4 — Reserved These bits are read as 0. The write value should be 0. R/W

b7, b6 POE3M[1:0] POE3 Mode

Select

b7 b6

0 0: Accepts a high-impedance request on the falling edge of the POE3# pin

input.

0 1: Accepts a high-impedance request when the POE3# pin input has been

sampled 16 times at PCLK/8 clock cycles and all are low level.

1 0: Accepts a high-impedance request when POE3# input has been sampled 16

times at PCLK/16 clock pulses and all are low level.

1 1: Accepts a high-impedance request when POE3# input has been sampled 16

times at PCLK/128 clock pulses and all are low level.

R/W*

1

b8 PIE1 Port Interrupt

Enable 1

0: OEI1 interrupt requests by the input level detection disabled

1: OEI1 interrupt requests by the input level detection enabled

R/W

b11 to b9 — Reserved These bits are read as 0. The write value should be 0. R/W

b12 POE0F POE0 Flag 0: Indicates that a high-impedance request has not been input to the POE0# pin.

1: Indicates that a high-impedance request has been input to the POE0# pin.

R/(W)

*

2

b13 POE1F POE1 Flag 0: Indicates that a high-impedance request has not been input to the POE1# pin.

1: Indicates that a high-impedance request has been input to the POE1# pin.

R/(W)

*

2

b14 — Reserved This bit is read as 0. The write value should be 0. R/W

b15 POE3F POE3 Flag 0: Indicates that a high-impedance request has not been input to the POE3# pin.

1: Indicates that a high-impedance request has been input to the POE3# pin.

R/(W)

*

2

Loading...

Loading...