R01UH0823EJ0100 Rev.1.00 Page 416 of 1823

Jul 31, 2019

RX23W Group 20. Event Link Controller (ELC)

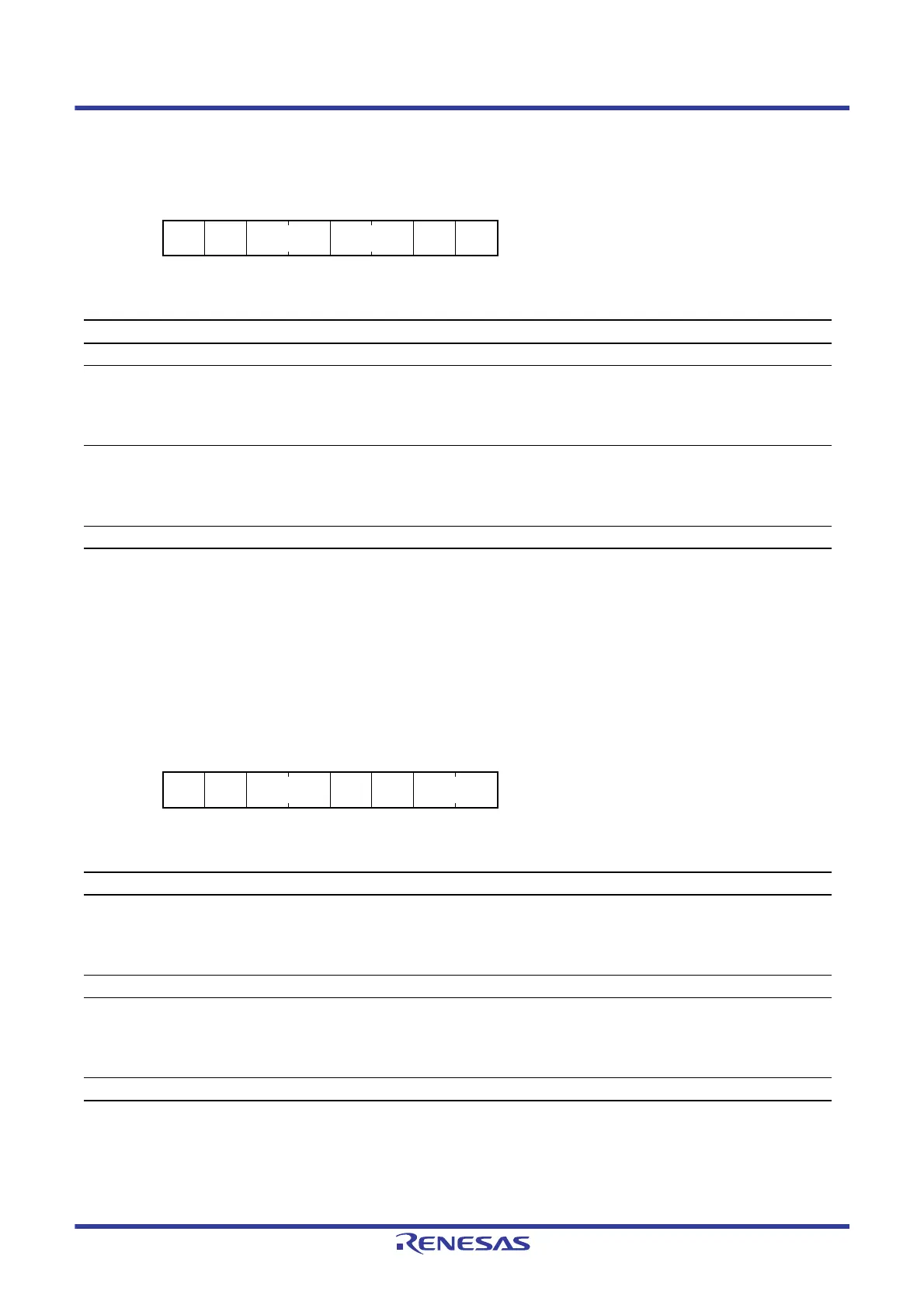

20.2.5 Event Link Option Setting Register C (ELOPC)

The ELOPC register specifies the operations of CMT1 and LPT when an event signal is input. Set 11b (event output is

disabled) when the ELC function is not used.

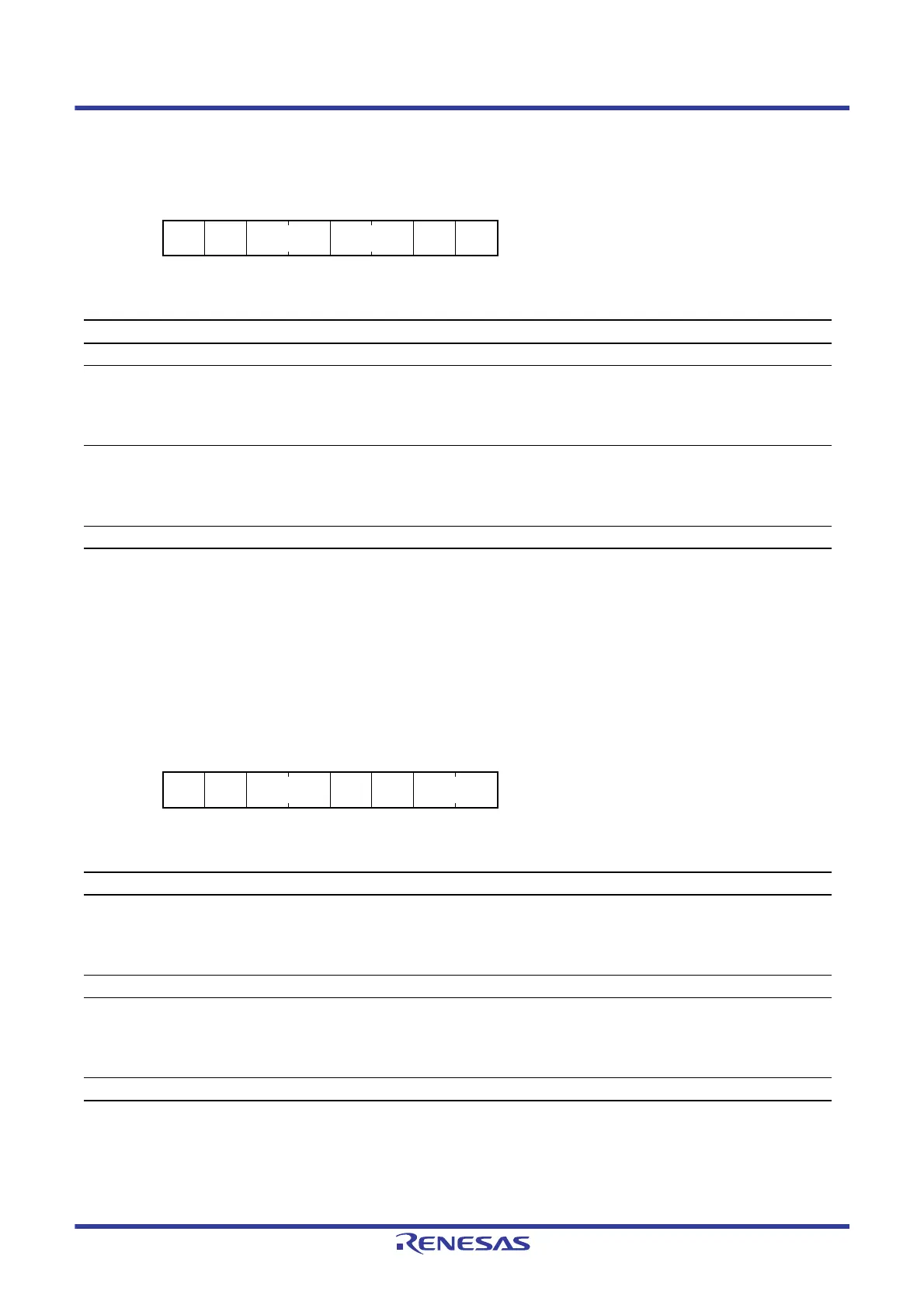

20.2.6 Event Link Option Setting Register D (ELOPD)

The ELOPD register specifies the operations of TMR0 and TMR2 when an event signal is input. Set 11b (event output is

disabled) when the ELC function is not used.

Address(es): ELC.ELOPC 0008 B121h

b7 b6 b5 b4 b3 b2 b1 b0

— — LPTMD[1:0] CMT1MD[1:0] — —

Value after reset:

11111111

Bit Symbol Bit Name Description R/W

b1, b0 — Reserved These bits are read as 1. The write value should be 1. R/W

b3, b2 CMT1MD[1:0] CMT1 Operation Select

b3 b2

0 0: Counting is started.

0 1: Counting is restarted.

1 0: Event counter

1 1: Event output is disabled.

R/W

b5, b4 LPTMD[1:0] LPT Operation Select

b5 b4

0 0: Output the compare match event to ICU as an interrupt

request

1 1: Event output is disabled.

Settings other than above are prohibited.

R/W

b7, b6 — Reserved These bits are read as 1. The write value should be 1. R/W

Address(es): ELC.ELOPD 0008 B122h

b7 b6 b5 b4 b3 b2 b1 b0

— — TMR2MD[1:0] — — TMR0MD[1:0]

Value after reset:

11111111

Bit Symbol Bit Name Description R/W

b1, b0 TMR0MD[1:0] TMR0 Operation Select

b1 b0

0 0: Counting is started.

0 1: Counting is restarted.

1 0: Event counter

1 1: Event output is disabled.

R/W

b3, b2 — Reserved These bits are read as 1. The write value should be 1. R/W

b5, b4 TMR2MD[1:0] TMR2 Operation Select

b5 b4

0 0: Counting is started.

0 1: Counting is restarted.

1 0: Event counter

1 1: Event output is disabled.

R/W

b7, b6 — Reserved These bits are read as 1. The write value should be 1. R/W

Loading...

Loading...