R01UH0823EJ0100 Rev.1.00 Page 851 of 1823

Jul 31, 2019

RX23W Group 31. Independent Watchdog Timer (IWDTa)

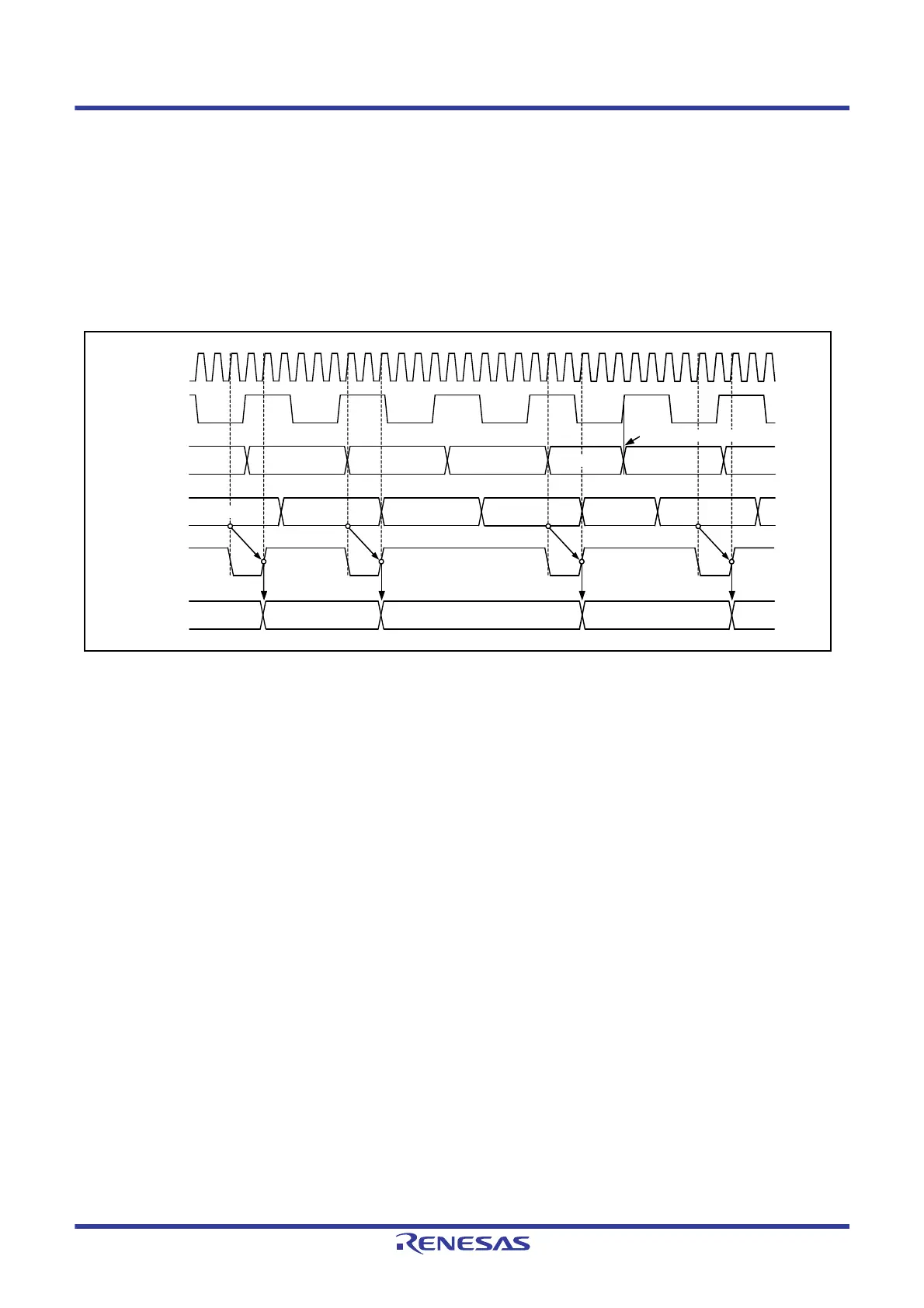

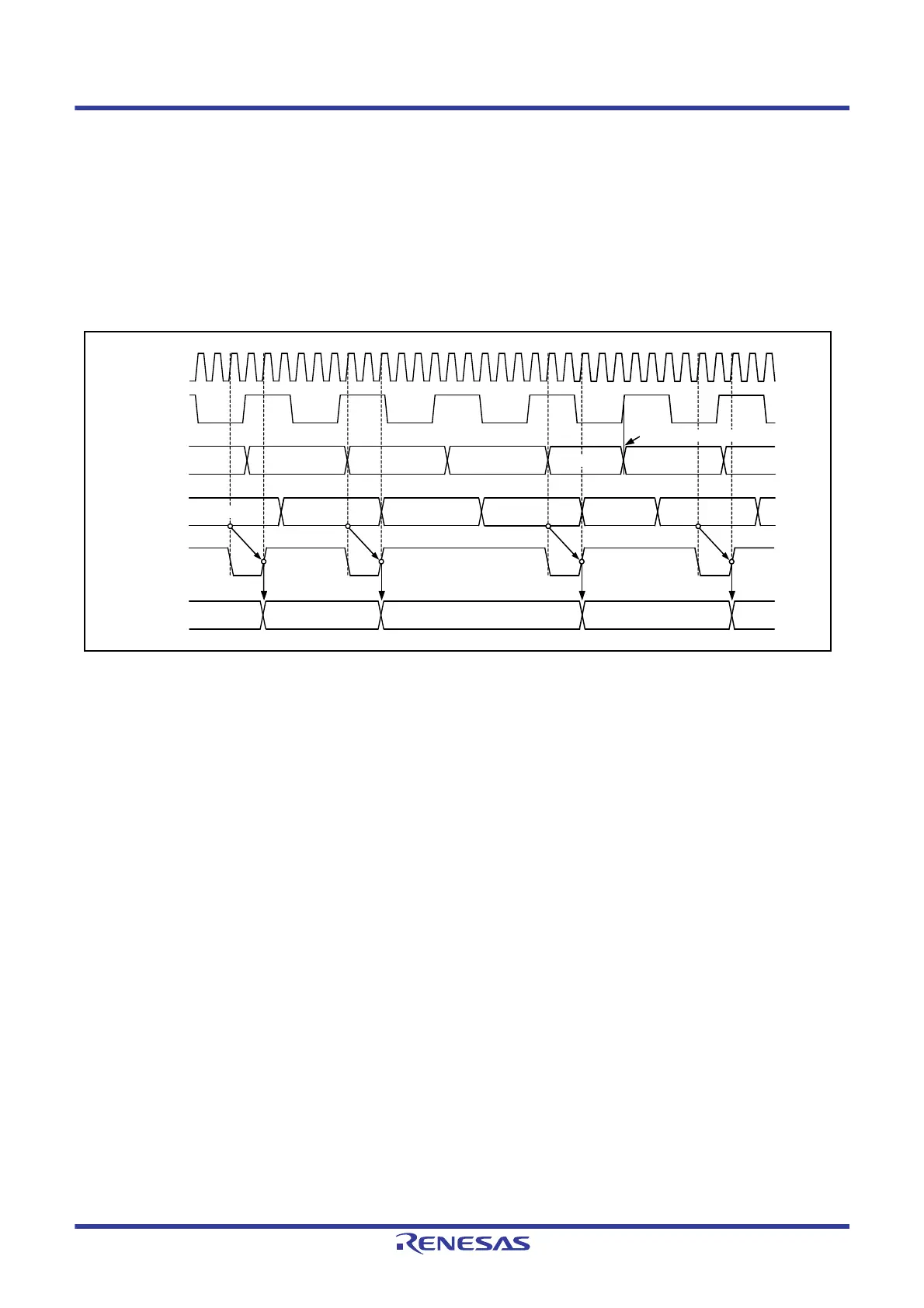

31.3.7 Reading the Counter Value

As the counter in IWDT-dedicated clock (IWDTCLK), the counter value cannot be read directly. The IWDT

synchronizes the counter value with the peripheral module clock (PCLK) and stores it in the IWDTSR.CNTVAL[13:0]

bits. Thus, the counter value can be checked indirectly through the IWDTSR.CNTVAL[13:0] bits.

Reading the counter value requires multiple PCLK clock cycles (up to four clock cycles), and the read counter value may

differ from the actual counter value by a value of one count.

Figure 31.7 shows the processing for reading the IWDT counter value when PCLK > IWDTCLK and clock divide ratio

= IWDTCLK.

Figure 31.7 Processing for Reading IWDT Counter Value

(IWDTCR.CKS[3:0] = 0000b, IWDTCR.TOPS[1:0] = 11b)

Peripheral module

clock (PCLK)

IWDT-dedicated

clock (IWDTCLK)

IWDTSR.CNTVAL

[13:0] read data

IWDTSR.CNTVAL

[13:0] read signal

(internal signal)

Bits

IWDTSR.CNTVAL

[13:0]

Counter value

n+1 n n-2

n+1 n n-1 n-2

n n-1 n-2 n-3

Refreshing

(after synchronization with IWDTCLK)

n+1

n-3

Loading...

Loading...