R01UH0823EJ0100 Rev.1.00 Page 1355 of 1823

Jul 31, 2019

RX23W Group 38. Serial Peripheral Interface (RSPIa)

38.2.14 RSPI Command Register m (SPCMDm) (m = 0 to 7)

x: Don’t care

Address(es): RSPI0.SPCMD0 0008 8390h, RSPI0.SPCMD1 0008 8392h, RSPI0.SPCMD2 0008 8394h,

RSPI0.SPCMD3 0008 8396h, RSPI0.SPCMD4 0008 8398h, RSPI0.SPCMD5 0008 839Ah,

RSPI0.SPCMD6 0008 839Ch, RSPI0.SPCMD7 0008 839Eh

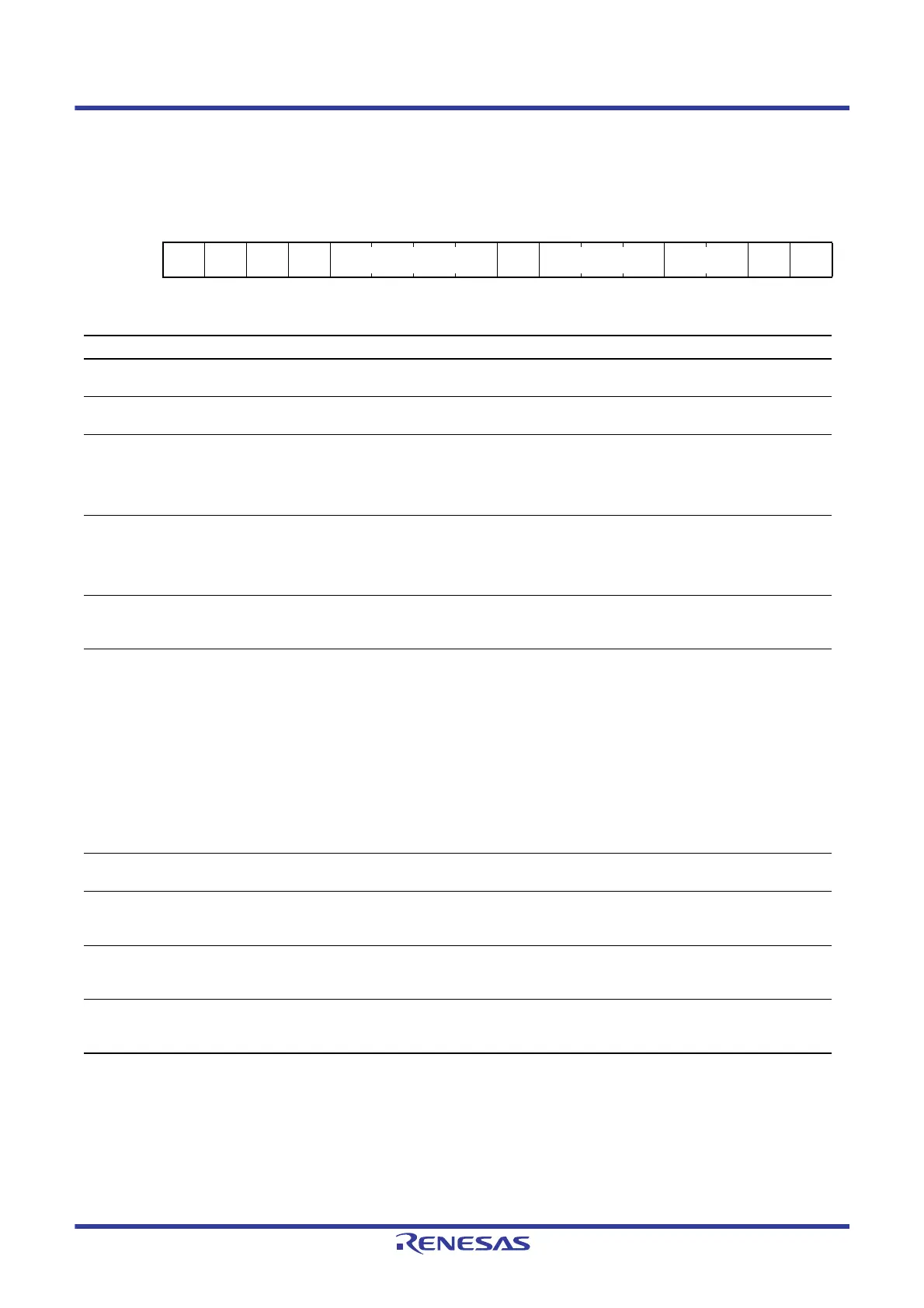

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

SCKDE

N

SLNDE

N

SPNDE

N

LSBF SPB[3:0] SSLKP SSLA[2:0] BRDV[1:0] CPOL CPHA

Value after reset:

0000011100001101

Bit Symbol Bit Name Description R/W

b0 CPHA RSPCK Phase Setting 0: Data sampling on odd edge, data variation on even edge

1: Data variation on odd edge, data sampling on even edge

R/W

b1 CPOL RSPCK Polarity Setting 0: RSPCK is low when idle

1: RSPCK is high when idle

R/W

b3, b2 BRDV[1:0] Bit Rate Division Setting

b3 b2

0 0: These bits select the base bit rate

0 1: These bits select the base bit rate divided by 2

1 0: These bits select the base bit rate divided by 4

1 1: These bits select the base bit rate divided by 8

R/W

b6 to b4 SSLA[2:0] SSL Signal Assertion Setting

b6 b4

000: SSL0

001: SSL1

011: SSL3

1 x x: Setting prohibited

R/W

b7 SSLKP SSL Signal Level Keeping 0: Negates all SSL signals upon completion of transfer

1: Keeps the SSL signal level from the end of transfer until the

beginning of the next access

R/W

b11 to b8 SPB[3:0] RSPI Data Length Setting

b11 b8

0100 to 0111: 8 bits

1000: 9 bits

1001: 10 bits

1010: 11 bits

1011: 12 bits

1100: 13 bits

1101: 14 bits

1110: 15 bits

1111: 16 bits

0000: 20 bits

0001: 24 bits

0010, 0011: 32 bits

R/W

b12 LSBF RSPI LSB First 0: MSB first

1: LSB first

R/W

b13 SPNDEN RSPI Next-Access Delay

Enable

0: A next-access delay of 1 RSPCK + 2 PCLK

1: A next-access delay is equal to the setting of the RSPI next-

access delay register (SPND)

R/W

b14 SLNDEN SSL Negation Delay Setting

Enable

0: An SSL negation delay of 1 RSPCK

1: An SSL negation delay is equal to the setting of the RSPI slave

select negation delay register (SSLND)

R/W

b15 SCKDEN RSPCK Delay Setting Enable 0: An RSPCK delay of 1 RSPCK

1: An RSPCK delay is equal to the setting of the RSPI clock delay

register (SPCKD)

R/W

Loading...

Loading...