R01UH0823EJ0100 Rev.1.00 Page 665 of 1823

Jul 31, 2019

RX23W Group 25. 16-Bit Timer Pulse Unit (TPUa)

25.2.2 Timer Mode Register (TMDR)

Note 1. Phase counting mode cannot be set for TPU0 and TPU3. A 0 should be written to bit 2 for them.

Note 2. These bits are reserved in TPU1, TPU2, TPU4, and TPU5. These bits are read as 0. The write value should be 0.

Note 3. In TPU0, TPU1, TPU2, and TPU5, which have no TIOCAn pin, these bits are reserved. These bits are read as 0. The write value

should be 0.

Note 4. In TPU0, TPU1, TPU2, TPU4, and TPU5, which have no TIOCCn, TIOCDn pin, these bits are reserved. These bits are read as

0. The write value should be 0.

TPUm.TMDR settings should be made while TPUm.TCNT operation is stopped.

BFA Bit (Buffer Operation A)

Specifies whether TPUm.TGRA (m = 0, 3) is to normally operate, or TPUm.TGRA and TPUm.TGRC (m = 0, 3) are to

be used together for buffer operation.

When TGRC is used as a buffer register, TGRC input capture/output compare is not generated.

BFB Bit (Buffer Operation B)

Specifies whether TPUm.TGRB (m = 0, 3) is to normally operate, or TPUm.TGRB and TPUm.TGRD (m = 0, 3) are to

be used together for buffer operation.

When TGRD is used as a buffer register, TGRD input capture/output compare is not generated.

ICSELB Bit (TGRB Input Capture Input Select)

Selects the input capture input for TPUm.TGRB (m = 3, 4).

This function allows measurement of high-level width and period of the input pulse on a TIOCAn input pin.

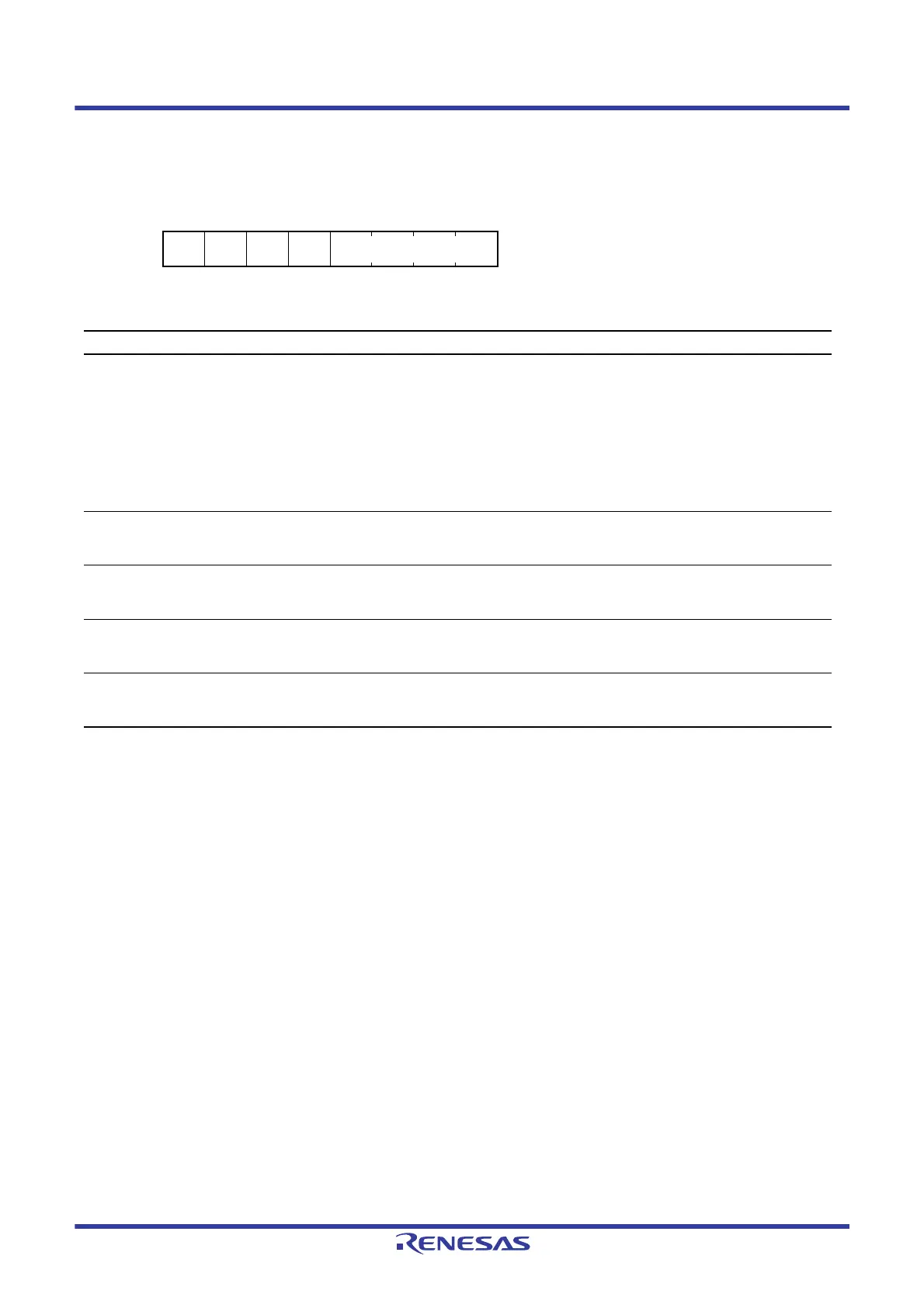

Address(es): TPU0.TMDR 0008 8111h, TPU1.TMDR 0008 8121h, TPU2.TMDR 0008 8131h,

TPU3.TMDR 0008 8141h, TPU4.TMDR 0008 8151h, TPU5.TMDR 0008 8161h

b7 b6 b5 b4 b3 b2 b1 b0

ICSEL

D

ICSELB BFB BFA MD[3:0]

Value after reset:

00000000

Bit Symbol Bit Name Description R/W

b3 to b0 MD[3:0] Mode Select

b3 b0

0 0 0 0: Normal operation

0 0 0 1: Setting prohibited

0 0 1 0: PWM mode 1

0 0 1 1: PWM mode 2

0 1 0 0: Phase counting mode 1*

1

0 1 0 1: Phase counting mode 2*

1

0 1 1 0: Phase counting mode 3*

1

0 1 1 1: Phase counting mode 4*

1

Settings other than above are prohibited.

R/W

b4 BFA Buffer Operation A*

2

0: TPUm.TGRA operates normally

1: TPUm.TGRA and TPUm.TGRC used together for buffer operation

(m = 0, 3)

R/W

b5 BFB Buffer Operation B*

2

0: TPUm.TGRB operates normally

1: TPUm.TGRB and TPUm.TGRD used together for buffer operation

(m = 0, 3)

R/W

b6 ICSELB TGRB Input Capture Input

Select*

3

0: Input capture input source is TIOCBn pin

1: Input capture input source is TIOCAn pin

(n = 3, 4)

R/W

b7 ICSELD TGRD Input Capture Input

Select*

4

0: Input capture input source is TIOCDn pin

1: Input capture input source is TIOCCn pin

(n = 3)

R/W

Loading...

Loading...