R01UH0823EJ0100 Rev.1.00 Page 277 of 1823

Jul 31, 2019

RX23W Group 15. Interrupt Controller (ICUb)

15.2.8 IRQ Control Register i (IRQCRi) (i = 0, 1, and 4 to 7)

Only change the settings of this register while the corresponding interrupt request enable bit is prohibiting the interrupt

request (IENj bit in IERm (m = 02h to 1Fh, j = 0 to 7) is 0). After changing the setting, clear the IR flag in IRn before

setting the interrupt enable bit. However, when the change is to the low level, the IR flag does not require clearing.

IRQMD[1:0] Bits (IRQ Detection Sense Select)

These bits select the interrupt detection sensing method of IRQi pin.

For the external pin interrupt detection setting, see

section 15.4.8, External Pin Interrupts.

Address(es): ICU.IRQCR0 0008 7500h, ICU.IRQCR1 0008 7501h, ICU.IRQCR4 0008 7504h to ICU.IRQCR7 0008 7507h

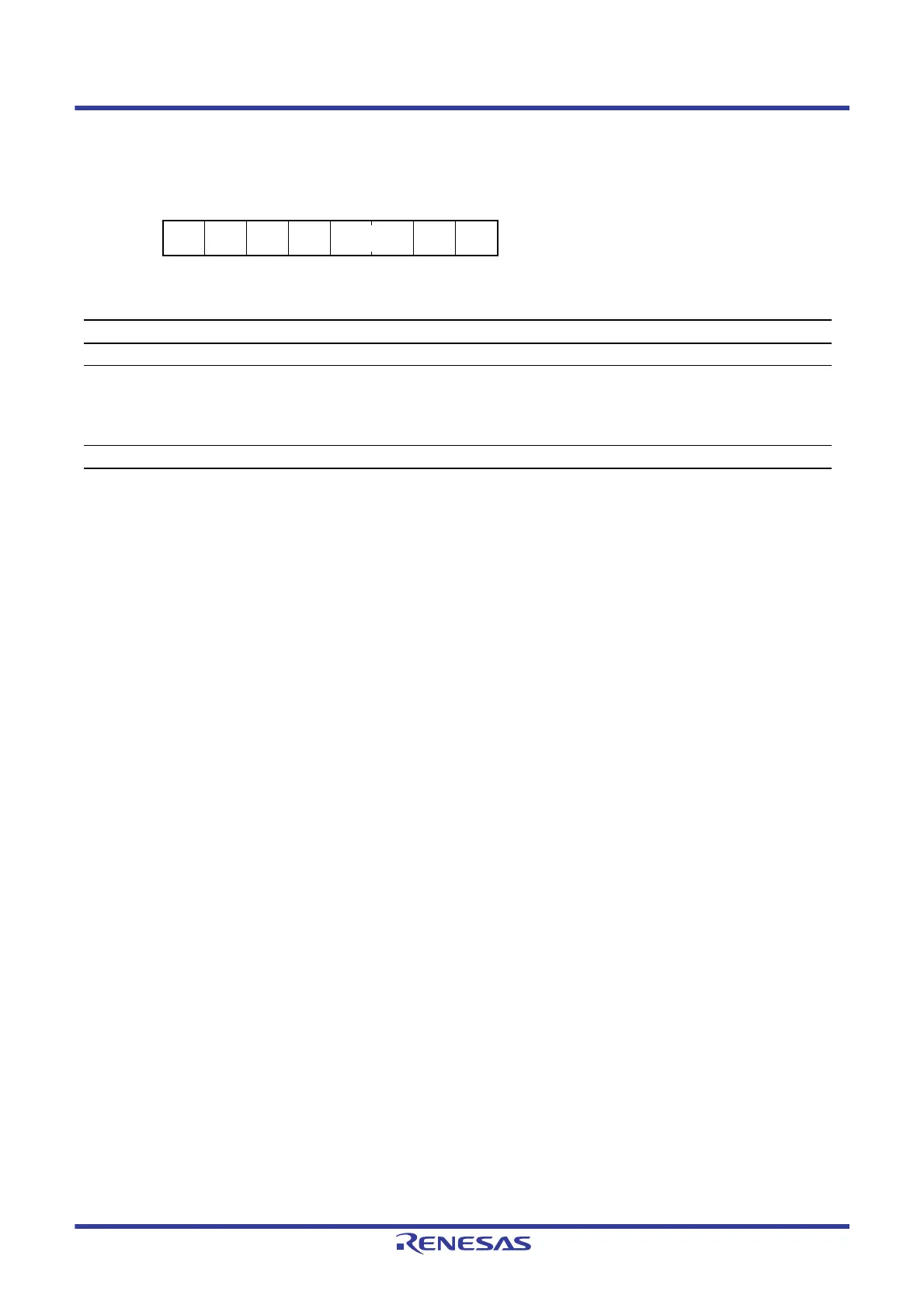

b7 b6 b5 b4 b3 b2 b1 b0

————IRQMD[1:0]——

Value after reset:

00000000

Bit Symbol Bit Name Description R/W

b1, b0 — Reserved These bits are read as 0. The write value should be 0. R/W

b3, b2 IRQMD[1:0] IRQ Detection Sense

Select

b3 b2

0 0: Low level

0 1: Falling edge

1 0: Rising edge

1 1: Rising and falling edges

R/W

b7 to b4 — Reserved These bits are read as 0. The write value should be 0. R/W

Loading...

Loading...