R01UH0823EJ0100 Rev.1.00 Page 840 of 1823

Jul 31, 2019

RX23W Group 31. Independent Watchdog Timer (IWDTa)

31.2.3 IWDT Status Register (IWDTSR)

Note 1. Only 0 can be written to clear the flag.

The IWDTSR register is initialized by the reset source of the IWDT. The IWDTSR register is not initialized by other

reset sources.

CNTVAL[13:0] Bits (Counter Value)

These bits are used to confirm the counter value of the counter, but note that the read value may differ from the actual

count by a value of one count.

UNDFF Flag (Underflow Flag)

This bit is used to confirm whether or not an underflow has occurred in the counter.

The value 1 indicates that the counter has underflowed. The value 0 indicates that the counter has not underflowed.

Write 0 to the UNDFF flag to set the value to 0. Writing 1 has no effect.

REFEF Flag (Refresh Error Flag)

This bit is used to confirm whether or not a refresh error (performing a refresh operation during a refresh-prohibited

period).

The value 1 indicates that a refresh error has occurred. The value 0 indicates that no refresh error has occurred.

Write 0 to the REFEF flag to set the value to 0. Writing 1 has no effect.

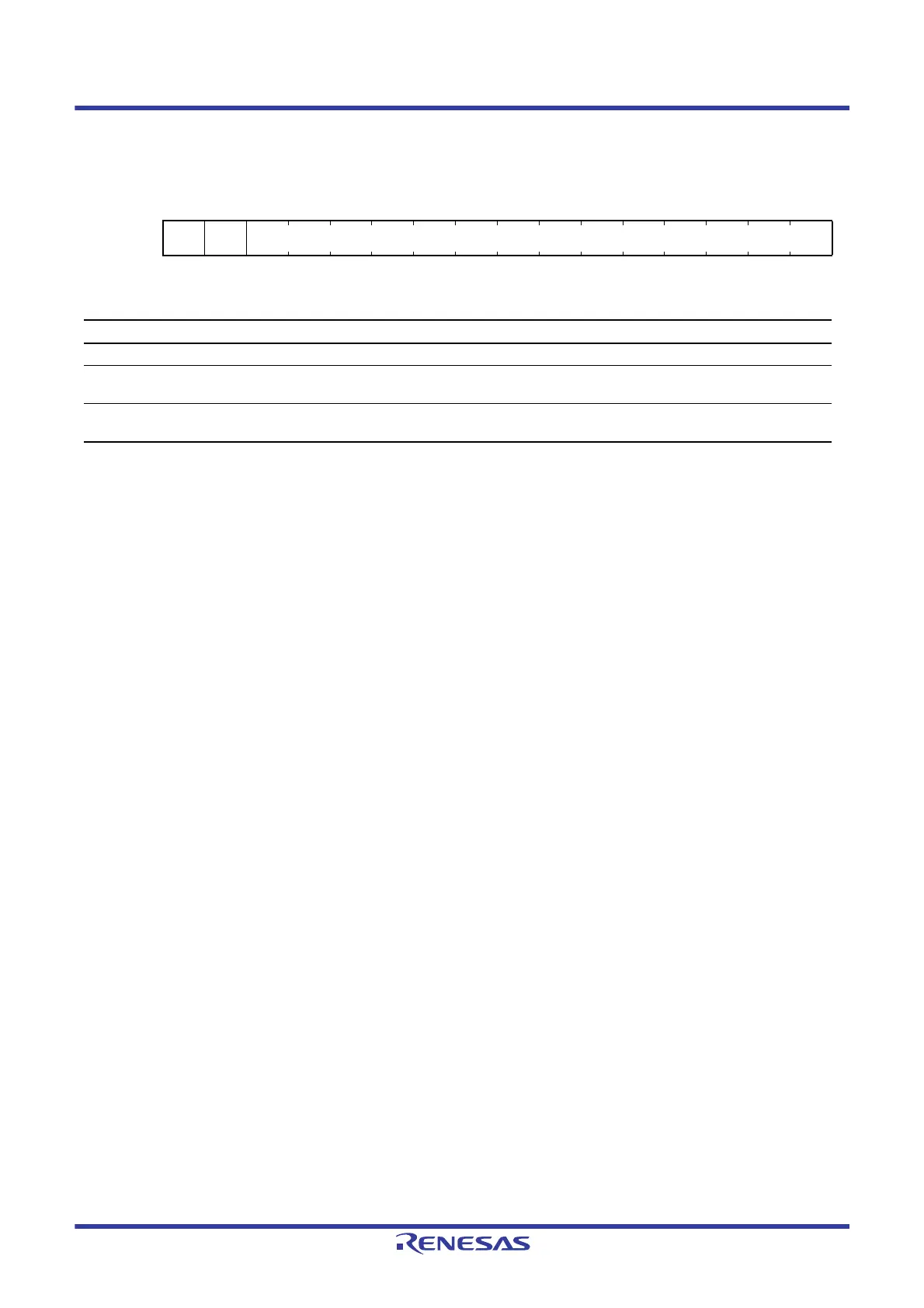

Address(es): IWDT.IWDTSR 0008 8034h

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

REFEF UNDFF CNTVAL[13:0]

Value after reset:

0000000000000000

Bit Symbol Bit Name Description R/W

b13 to b0 CNTVAL[13:0] Counter Value Value counted by the counter R

b14 UNDFF Underflow Flag 0: No underflow occurred

1: Underflow occurred

R/(W)

*

1

b15 REFEF Refresh Error Flag 0: No refresh error occurred

1: Refresh error occurred

R/(W)

*

1

Loading...

Loading...