R01UH0823EJ0100 Rev.1.00 Page 1508 of 1823

Jul 31, 2019

RX23W Group 43. Capacitive Touch Sensing Unit (CTSU)

43.2.15 CTSU Sensor Offset Register 1 (CTSUSO1)

Note 1. The CTSUSDPA[4:0] bits should not be set to 00000b while the high-pass noise reduction function is turned off

(CTSUSDPRS.CTSUSOFF bit = 1) in mutual capacitance full scan mode (CTSUCR1.CTSUMD[1:0] bits = 11b).

Write first to the CTSUSSC register, then CTSUSO0 register, and then CTSUSO1 register after a CTSUWR interrupt is

generated. Write operation to the CTSUSO1 register causes a transition to Status 3. Thus, set all the bits in a single

setting when writing to the CTSUSO1 register.

Address(es): CTSU.CTSUSO1 000A 0916h

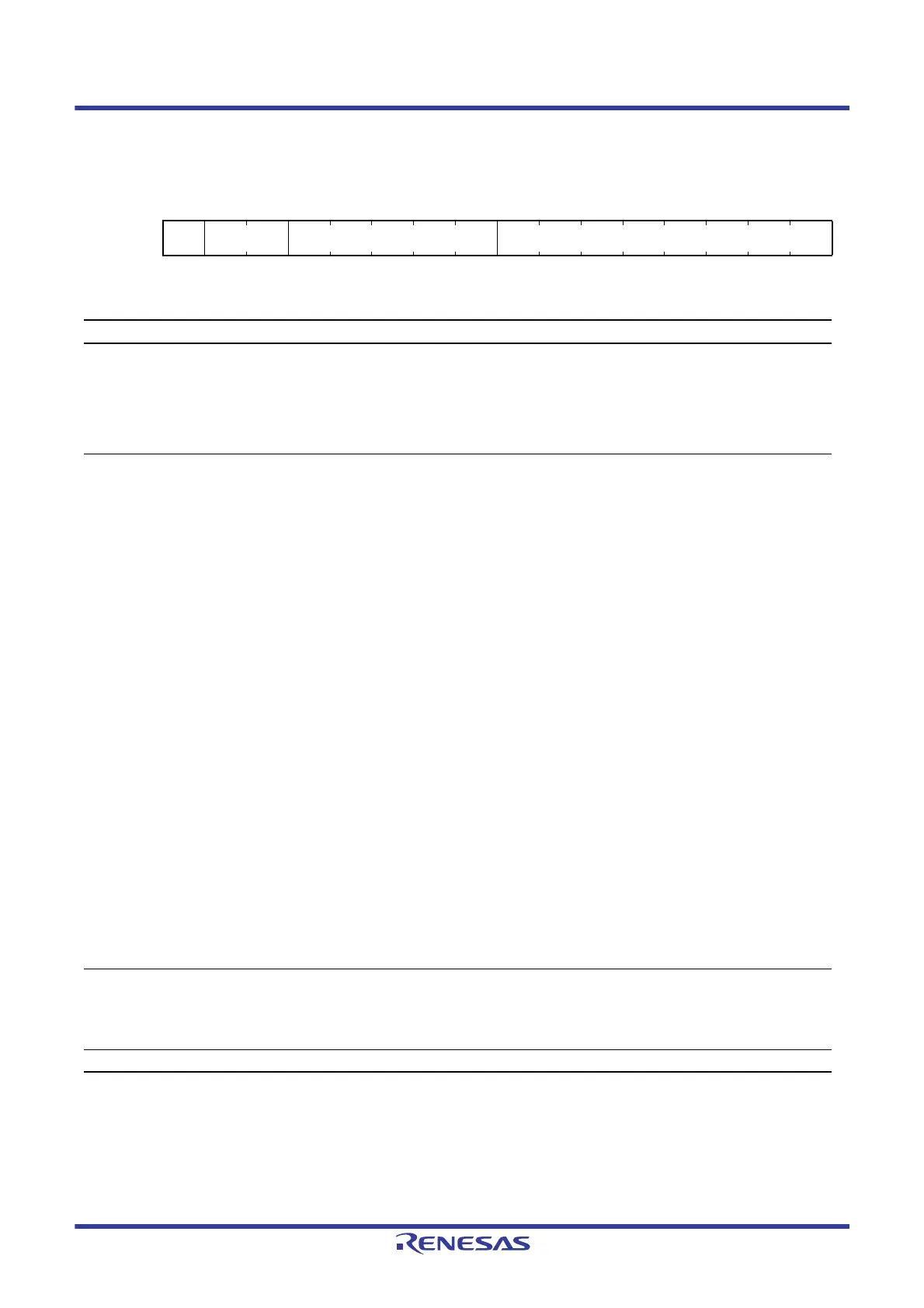

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

— CTSUICOG[1:0] CTSUSDPA[4:0] CTSURICOA[7:0]

Value after reset:

0000000000000000

Bit Symbol Bit Name Description R/W

b7 to b0 CTSURICOA[7:0] CTSU Reference ICO Current

Adjustment

b7 b0

0 0 0 0 0 0 0 0: Input current amount 0

0 0 0 0 0 0 0 1: Input current amount 1

0 0 0 0 0 0 1 0: Input current amount 2

::

1 1 1 1 1 1 1 0: Input current amount 254

1 1 1 1 1 1 1 1: Input current amount maximum

R/W

b12 to b8 CTSUSDPA[4:0] CTSU Base Clock Setting

b12 b8

0 0 0 0 0: Operating clock divided by 2*

1

0 0 0 0 1: Operating clock divided by 4

0 0 0 1 0: Operating clock divided by 6

0 0 0 1 1: Operating clock divided by 8

0 0 1 0 0: Operating clock divided by 10

0 0 1 0 1: Operating clock divided by 12

0 0 1 1 0: Operating clock divided by 14

0 0 1 1 1: Operating clock divided by 16

0 1 0 0 0: Operating clock divided by 18

0 1 0 0 1: Operating clock divided by 20

0 1 0 1 0: Operating clock divided by 22

0 1 0 1 1: Operating clock divided by 24

0 1 1 0 0: Operating clock divided by 26

0 1 1 0 1: Operating clock divided by 28

0 1 1 1 0: Operating clock divided by 30

0 1 1 1 1: Operating clock divided by 32

1 0 0 0 0: Operating clock divided by 34

1 0 0 0 1: Operating clock divided by 36

1 0 0 1 0: Operating clock divided by 38

1 0 0 1 1: Operating clock divided by 40

1 0 1 0 0: Operating clock divided by 42

1 0 1 0 1: Operating clock divided by 44

1 0 1 1 0: Operating clock divided by 46

1 0 1 1 1: Operating clock divided by 48

1 1 0 0 0: Operating clock divided by 50

1 1 0 0 1: Operating clock divided by 52

1 1 0 1 0: Operating clock divided by 54

1 1 0 1 1: Operating clock divided by 56

1 1 1 0 0: Operating clock divided by 58

1 1 1 0 1: Operating clock divided by 60

1 1 1 1 0: Operating clock divided by 62

1 1 1 1 1: Operating clock divided by 64

R/W

b14, b13 CTSUICOG[1:0] CTSU ICO Gain Adjustment

b14 b13

0 0: 100% gain

0 1: 66% gain

1 0: 50% gain

1 1: 40% gain

R/W

b15 — Reserved This bit is read as 0. The write value should be 0. R/W

Loading...

Loading...