R01UH0823EJ0100 Rev.1.00 Page 344 of 1823

Jul 31, 2019

RX23W Group 18. DMA Controller (DMACA)

18.2.5 DMA Transfer Mode Register (DMTMD)

Note 1. DMAC activation source is selected using the DMRSRm registers of the ICU. For details on DMAC activation sources, see

Table 15.3, Interrupt Vector Table in section 15, Interrupt Controller (ICUb).

DTS[1:0] Bits (Repeat Area Select)

DTS[1:0] select either the source or destination as the repeat area in repeat or block transfer mode. In normal transfer

mode, setting these bits is invalid.

Address(es): DMAC0.DMTMD 0008 2010h, DMAC1.DMTMD 0008 2050h, DMAC2.DMTMD 0008 2090h, DMAC3.DMTMD 0008 20D0h

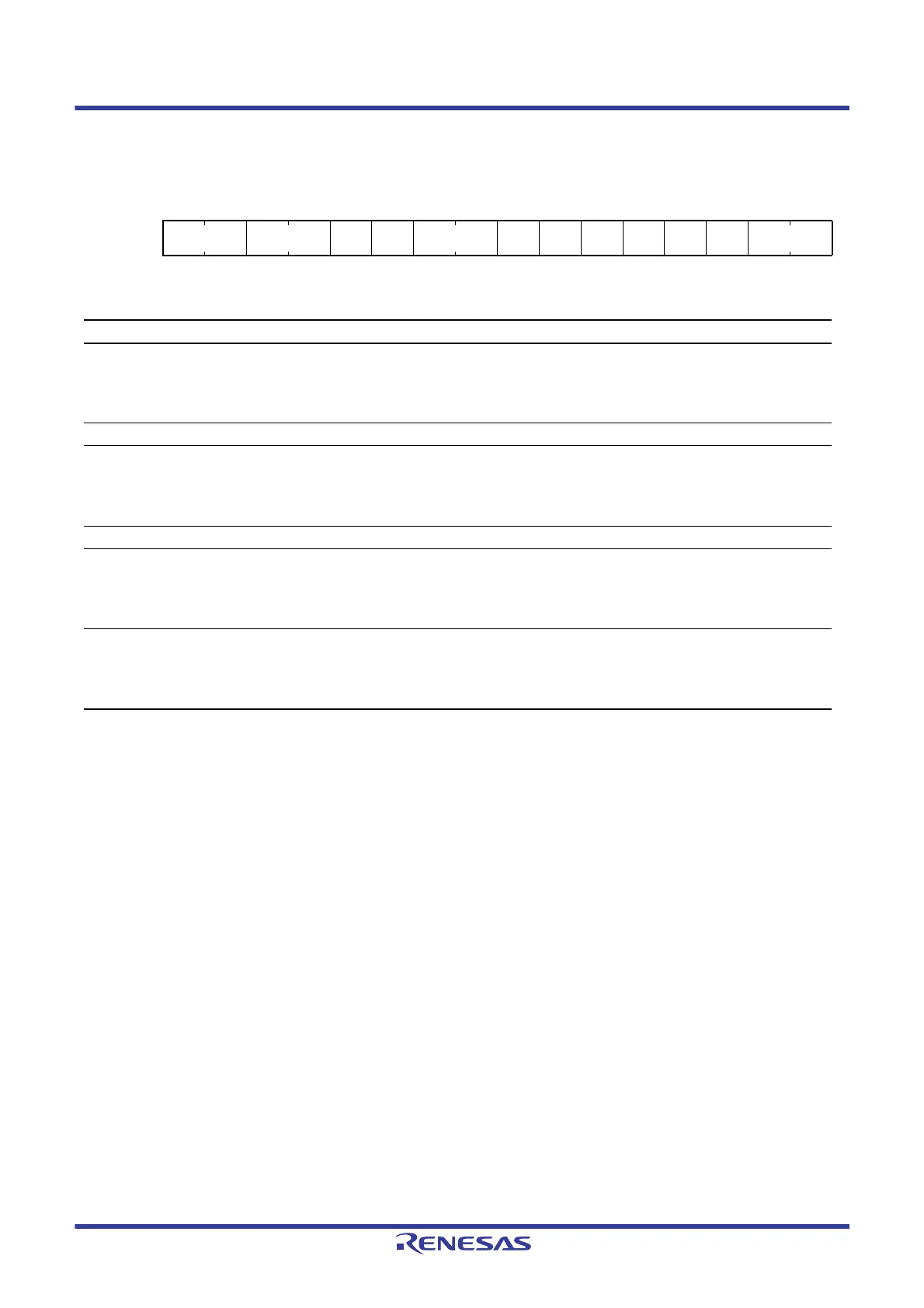

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

MD[1:0] DTS[1:0] —— SZ[1:0] ——————DCTG[1:0]

Value after reset:

0000000000000000

Bit Symbol Bit Name Description R/W

b1, b0 DCTG[1:0] DMA Request Source

Select

b1 b0

0 0: Software

0 1: Interrupts*

1

from peripheral modules or external interrupt input pins

1 0: Setting prohibited

1 1: Setting prohibited

R/W

b7 to b2 — Reserved These bits are read as 0. The write value should be 0. R/W

b9, b8 SZ[1:0] Transfer Data Size

Select

b9 b8

0 0: 8 bits

0 1: 16 bits

1 0: 32 bits

1 1: Setting prohibited

R/W

b11, b10 — Reserved These bits are read as 0. The write value should be 0. R/W

b13, b12 DTS[1:0] Repeat Area Select

b13 b12

0 0: The destination is specified as the repeat area or block area.

0 1: The source is specified as the repeat area or block area.

1 0: The repeat area or block area is not specified.

1 1: Setting prohibited

R/W

b15, b14 MD[1:0] Transfer Mode Select

b15 b14

0 0: Normal transfer

0 1: Repeat transfer

1 0: Block transfer

1 1: Setting prohibited

R/W

Loading...

Loading...