R01UH0823EJ0100 Rev.1.00 Page 420 of 1823

Jul 31, 2019

RX23W Group 20. Event Link Controller (ELC)

20.2.10 Event Link Port Setting Register m (PELm) (m = 0 to 3)

x: Don’t care

The PELm register specifies the single port, the operation upon an event signal input, and the conditions of event

generation. This MCU can specify a total of four bits in port B and port E to respective single ports.

Specify the I/O direction of the port by the corresponding bit in the PDR register.

Address(es): ELC.PEL0 0008 B129h, ELC.PEL1 0008 B12Ah, ELC.PEL2 0008 B12Bh, ELC.PEL3 0008 B12Ch

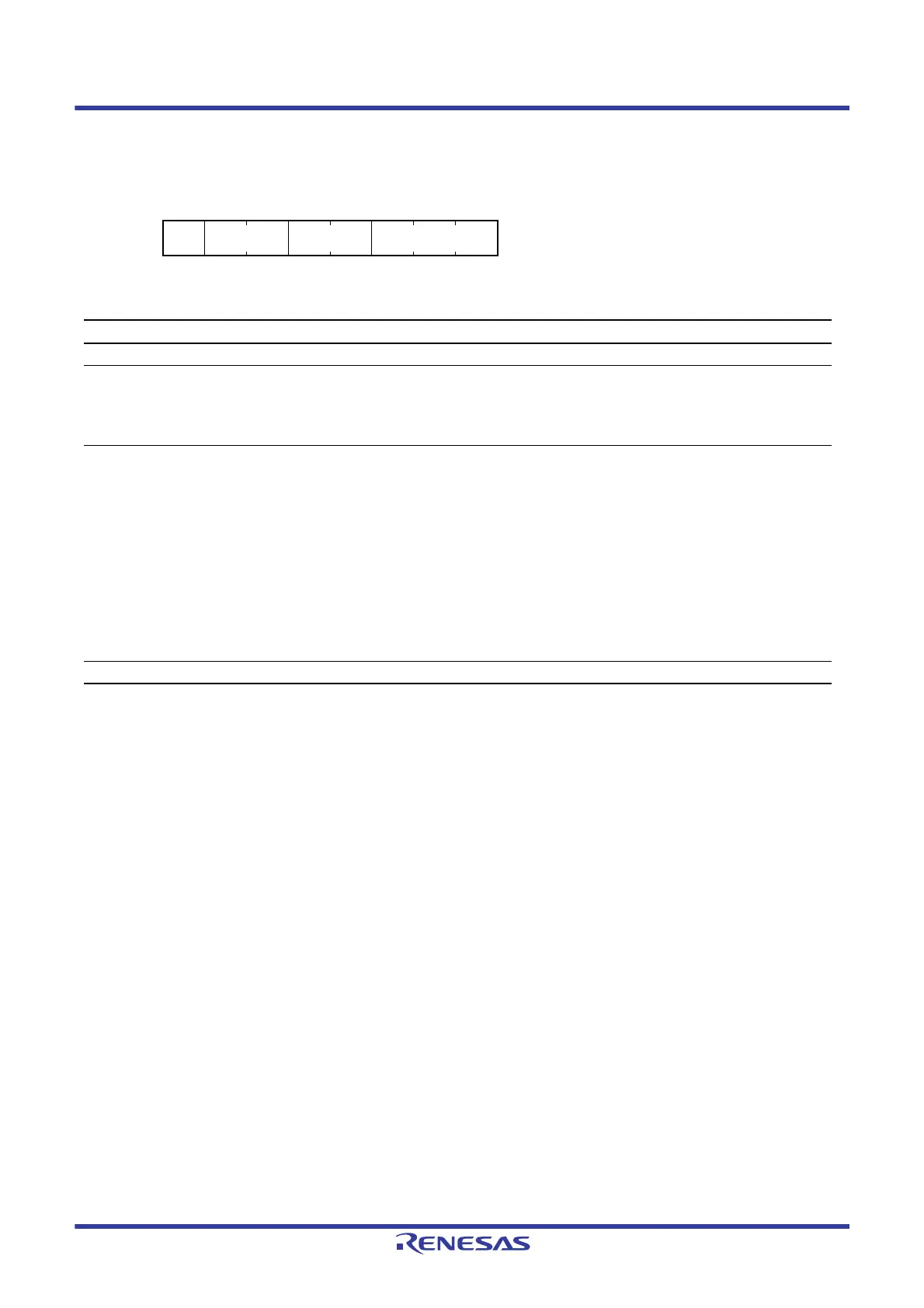

b7 b6 b5 b4 b3 b2 b1 b0

— PSM[1:0] PSP[1:0] PSB[2:0]

Value after reset:

10000000

Bit Symbol Bit Name Description R/W

b2 to b0 PSB[2:0] Bit Number Specification Set a bit number for a port to be specified as a single port. R/W

b4, b3 PSP[1:0] Port Number Specification

b4 b3

0 0: Setting disabled

0 1: Port B (corresponding to PGR1)

1 0: Port E (corresponding to PGR2)

1 1: Setting prohibited

R/W

b6, b5 PSM[1:0] Event Link Specification

For the output port, specify the data to be output from the

port.

b6 b5

0 0: Low is output when an event signal is input.

0 1: High is output when an event signal is input.

1 x: The output is toggled (inverted) when an event signal is

input.

For the input port, select the edge on which the event signal

is to be output.

b6 b5

0 0: Event signal is output upon detection of the rising edge.

0 1: Event signal is output upon detection of the falling edge.

1 x: Event signal is output upon detection of both the rising

and falling edges.

R/W

b7 — Reserved This bit is read as 1. The write value should be 1. R/W

Loading...

Loading...