R01UH0823EJ0100 Rev.1.00 Page 897 of 1823

Jul 31, 2019

RX23W Group 32. USB 2.0 Host/Function Module (USBc)

32.2.29 Pipe Cycle Control Register (PIPEPERI)

Note 1. Modify the IITV[2:0] bits while the PIPEnCTR.PID[1:0] bits are 00b (NAK). To modify these bits after modifying the

PIPEnCTR.PID[1:0] bits for the selected pipe from 01b (BUF) to 00b (NAK), check that the PIPEnCTR.PBUSY flag is 0.

However, if the USB changes the PID[1:0] bits to 00b (NAK), the PBUSY flag does not need to be checked by software.

The PIPEPERI register selects whether the buffer is flushed or not when an interval error occurred during isochronous IN

transfer, and sets the interval error detection interval for PIPE1 to PIPE9.

IITV[2:0] Bits (Interval Error Detection Interval)

Before modifying the IITV[2:0] bits after USB communication has been completed with the IITV[2:0] bits set to a

certain value, set the PID[1:0] bits to 00b (NAK) and then set the PIPEnCTR.ACLRM bit to 1 to initialize the interval

timer.

The IITV[2:0] bits are invalid for PIPE3 to PIPE5; set the IITV[2:0] bits to 000b for PIPE3 to PIPE5.

IFIS Bit (Isochronous IN Buffer Flush)

Specifies whether to flush the buffer when the pipe selected by the PIPESEL.PIPESEL[3:0] bits (selected pipe) is used

for isochronous IN transfers.

When the function controller is selected and the selected pipe is for isochronous IN transfers, the USB automatically

clears the FIFO buffer when the USB fails to receive the IN token from the USB host within the interval set by the

IITV[2:0] bits in terms of frames.

In double buffer mode (the PIPECFG.DBLB bit = 1), the USB only clears the data in the plane used earlier.

The USB clears the FIFO buffer on receiving the SOF packet immediately after the frame in which the USB has expected

to receive the IN token. Even if the SOF packet is damaged, the USB also clears the FIFO buffer at the right timing to

receive the SOF packet by using the internal interpolation function.

When the host controller is selected, set the IITV[2:0] bits to 000b.

When the selected pipe is not for isochronous transfer, set the IITV[2:0] bits to 000b.

Address(es): 000A 006Eh

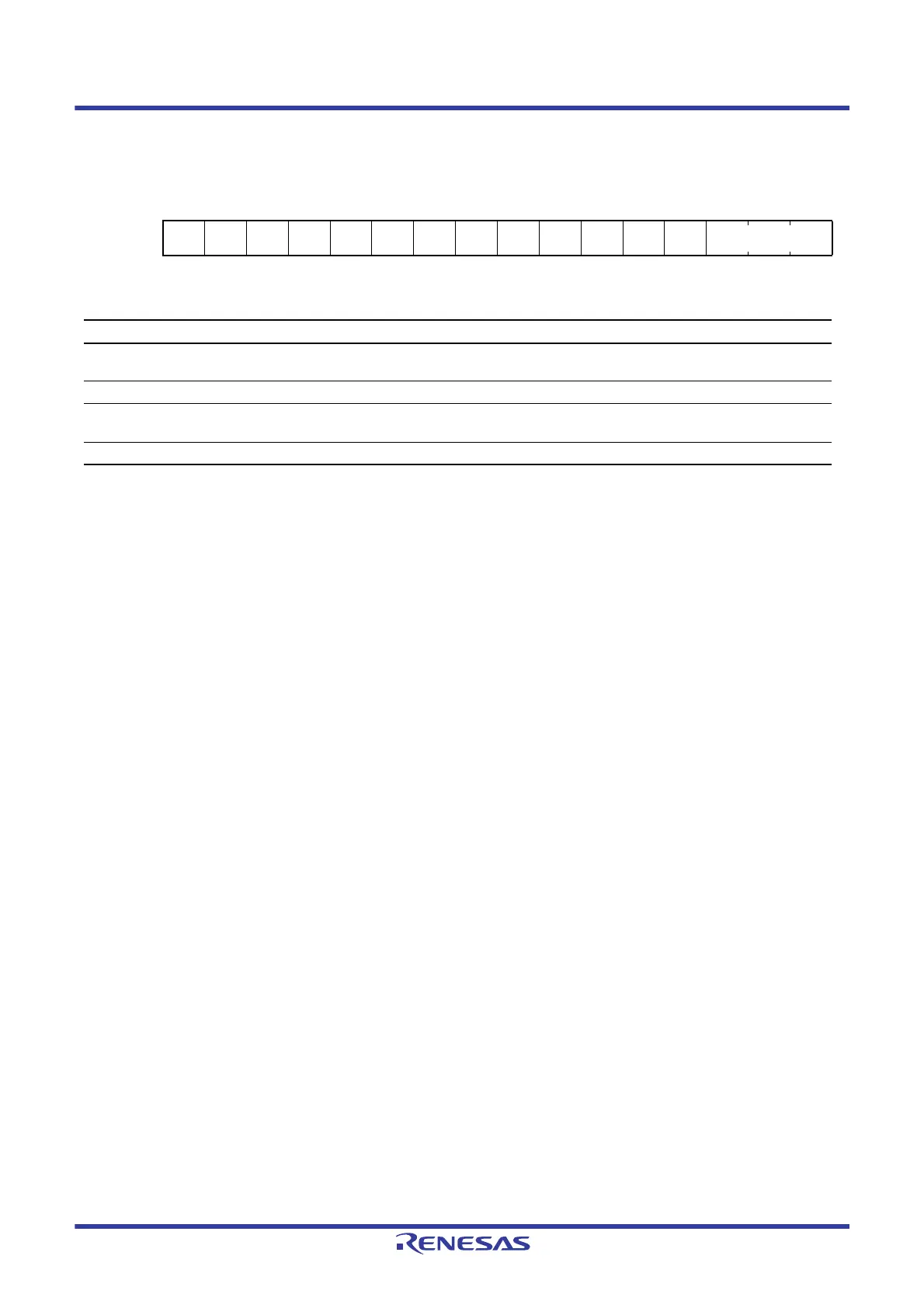

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

———IFIS————————— IITV[2:0]

Value after reset:

0000000000000000

Bit Symbol Bit Name Description R/W

b2 to b0 IITV[2:0] Interval Error Detection Interval

*

1

Specify the interval error detection timing for the selected pipe in

terms of frames, which is expressed as nth power of 2.

R/W

b11 to b3 — Reserved These bits are read as 0. The write value should be 0. R/W

b12 IFIS Isochronous IN Buffer Flush 0: The buffer is not flushed.

1: The buffer is flushed.

R/W

b15 to b13 — Reserved These bits are read as 0. The write value should be 0. R/W

Loading...

Loading...