R01UH0823EJ0100 Rev.1.00 Page 756 of 1823

Jul 31, 2019

RX23W Group 27. Compare Match Timer (CMT)

27.2.3 Compare Match Timer Control Register (CMCR)

CKS[1:0] Bits (Clock Select)

These bits select the count source from four frequency dividing clocks obtained by dividing the peripheral module clock

(PCLK).

When the CMSTRm.STRn (m = 0, 1; n = 0 to 3) bit is set to 1, the CMCNT counter starts counting up on the clock

selected with the CKS[1:0] bits.

CMIE Bit (Compare Match Interrupt Enable)

The CMIE bit enables or disables compare match interrupt (CMIn) (n = 0 to 3) generation when the CMCNT counter and

the CMCOR register values match.

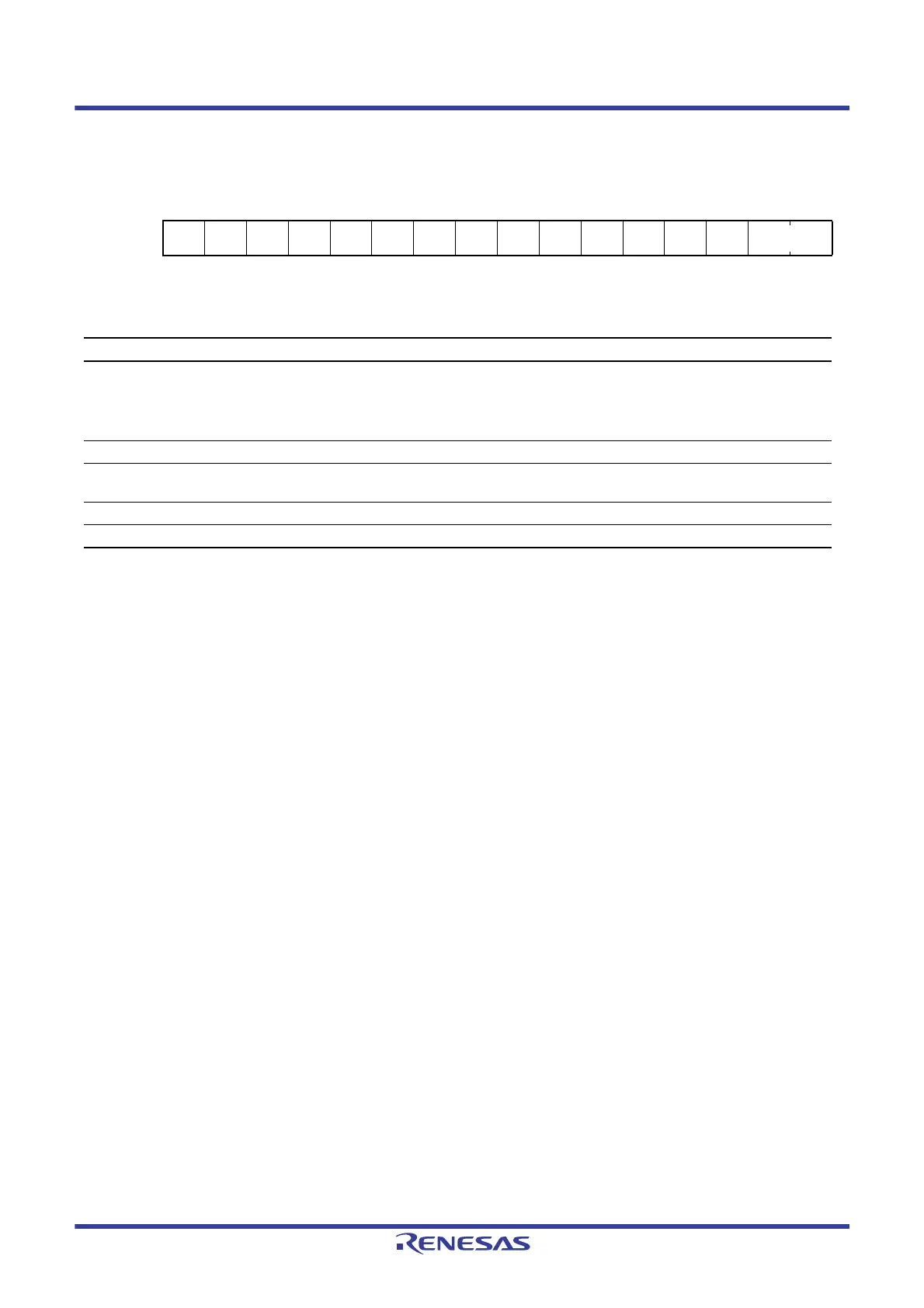

Address(es): CMT0.CMCR 0008 8002h, CMT1.CMCR 0008 8008h, CMT2.CMCR 0008 8012h, CMT3.CMCR 0008 8018h

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

—————————CMIE———— CKS[1:0]

Value after reset:

00000000x0000000

x: Undefined

Bit Symbol Bit Name Description R/W

b1, b0 CKS[1:0] Clock Select

b1 b0

0 0: PCLK/8

0 1: PCLK/32

1 0: PCLK/128

1 1: PCLK/512

R/W

b5 to b2 — Reserved These bits are read as 0. The write value should be 0. R/W

b6 CMIE Compare Match Interrupt

Enable

0: Compare match interrupt (CMIn) disabled

1: Compare match interrupt (CMIn) enabled

R/W

b7 — Reserved This bit is read as undefined. The write value should be 1. R/W

b15 to b8 — Reserved These bits are read as 0. The write value should be 0. R/W

Loading...

Loading...