R01UH0823EJ0100 Rev.1.00 Page 972 of 1823

Jul 31, 2019

RX23W Group 33. Serial Communications Interface (SCIg, SCIh)

33.2.5 Transmit Data Register H, L, HL (TDRH, TDRL, TDRHL)

Transmit Data Register H (TDRH)

Transmit Data Register L (TDRL)

Transmit Data Register HL (TDRHL)

TDRH and TDRL are 8-bit registers that store transmit data. Use these registers when asynchronous mode and 9-bit data

length are selected.

TDRL is the shadow register of TDR; i.e. access to TDRL is equivalent to access to TDR.

When empty space is detected in the TSR register, the transmit data stored in the TDRH and TDRL registers is

transferred to TSR; i.e., transmitting is started.

The TSR, TDRH and TDRL registers have a double-buffered construction to realize continuous reception. When the

next data to be transmitted is stored in the TDRL register after one frame of data has been transmitted, the transmitting

operation is continued by transfer to the TSR register.

The CPU can read and write to the TDRH and TDRL registers. Bits 0 to 7 in RDRH are fixed to 1. These bits are read as

1. The write value should be 1.

Writing transmit data to the TDRH and TDRL registers should be performed only once in the order from TDRH to

TDRL when a transmit data empty interrupt (TXI) request is issued.

The TDRHL register can be accessed in 16-bit units.

33.2.6 Transmit Shift Register (TSR)

TSR is a shift register that transmits serial data.

To perform serial data transmission, the SCI first automatically transfers transmit data from TDR to TSR, and then sends

the data to the TXDn pin.

TSR cannot be directly accessed by the CPU.

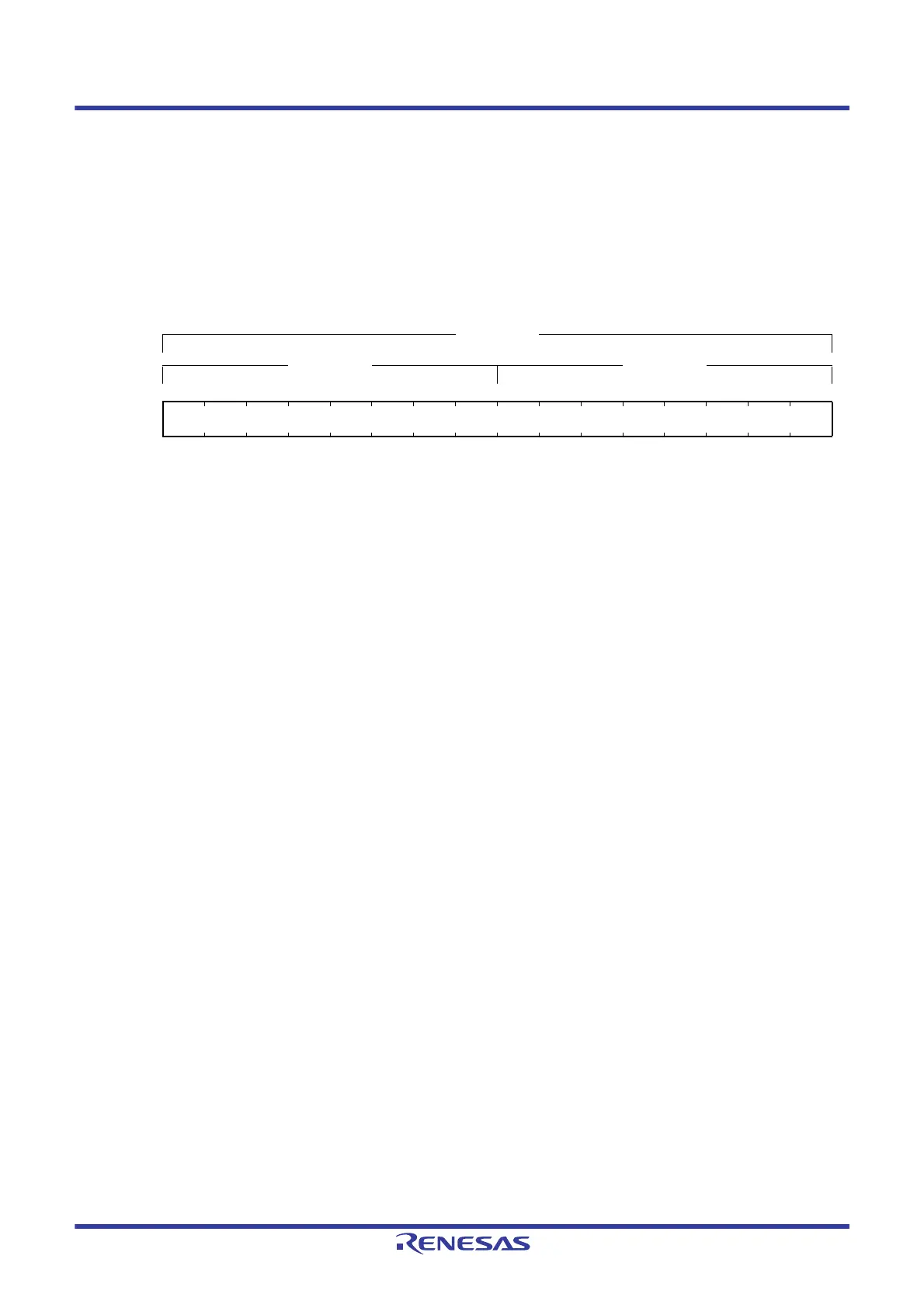

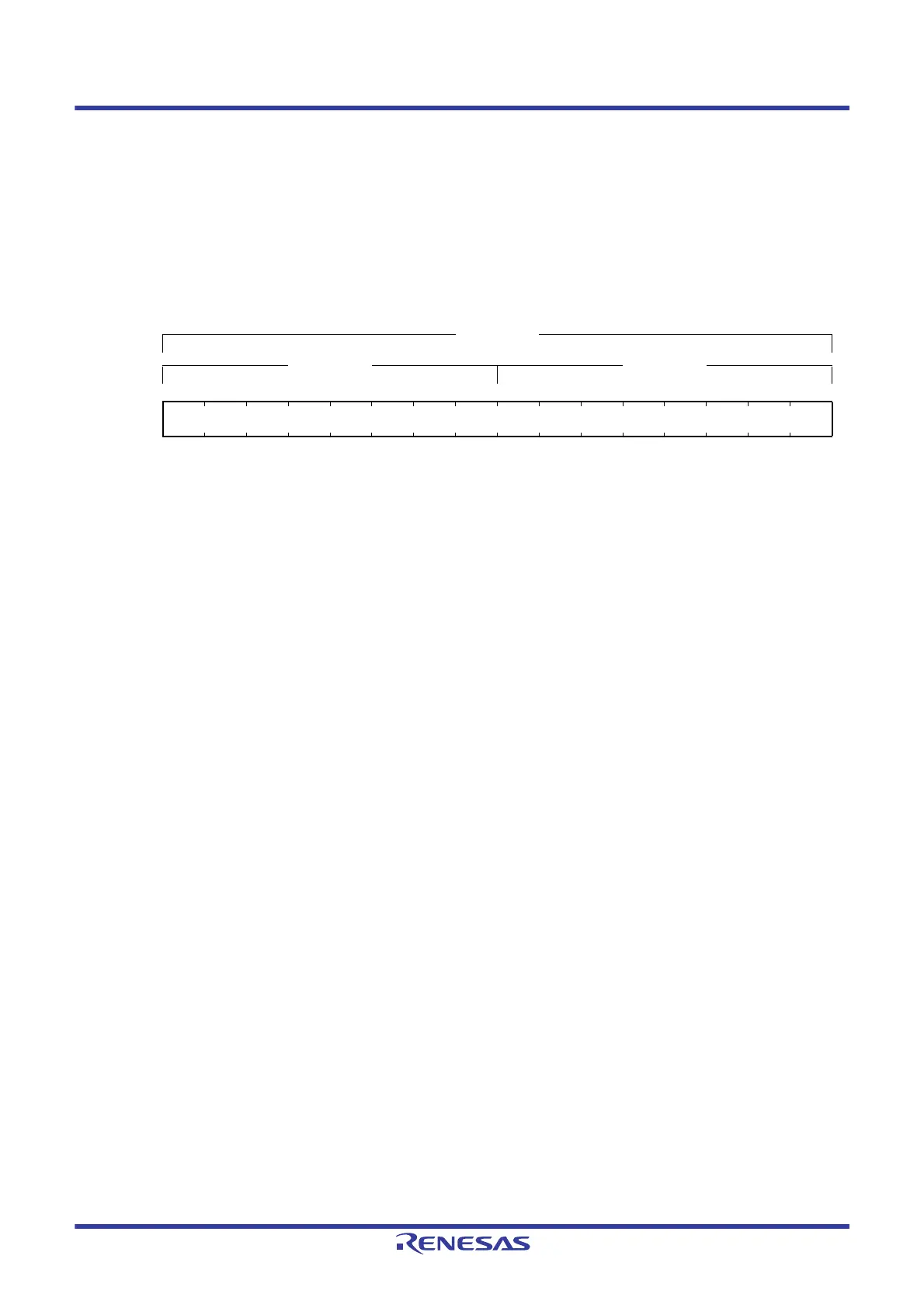

Address(es): SCI1.TDRH 0008 A02Eh, SCI5.TDRH 0008 A0AEh, SCI8.TDRH 0008 A10Eh, SCI12.TDRH 0008 B30Eh

Address(es): SCI1.TDRL 0008 A02Fh, SCI5.TDRL 0008 A0AFh, SCI8.TDRL 0008 A10Fh, SCI12.TDRL 0008 B30Fh

Address(es): SCI1.TDRHL 0008 A02Eh, SCI5.TDRHL 0008 A0AEh, SCI8.TDRHL 0008 A10Eh, SCI12.TDRHL 0008 B30Eh

TDRHL

TDRH TDRL

b7 b6 b5 b4 b3 b2 b1 b0 b7 b6 b5 b4 b3 b2 b1 b0

Value after reset:

1111111111111111

Loading...

Loading...