R01UH0823EJ0100 Rev.1.00 Page 831 of 1823

Jul 31, 2019

RX23W Group 30. Watchdog Timer (WDTA)

30.3.2 Control over Writing to the WDTCR and WDTRCR Registers

Writing to the WDTCR or WDTRCR register is only possible once between the release from the reset state and the first

refresh operation.

After a refresh operation (counting starts) or by writing to the WDTCR or WDTRCR register, the protection signal in the

WDT becomes 1 to protect the WDTCR and WDTRCR registers against subsequent attempts at writing.

This protection is released by the reset source of the WDT. With other reset sources, the protection is not released.

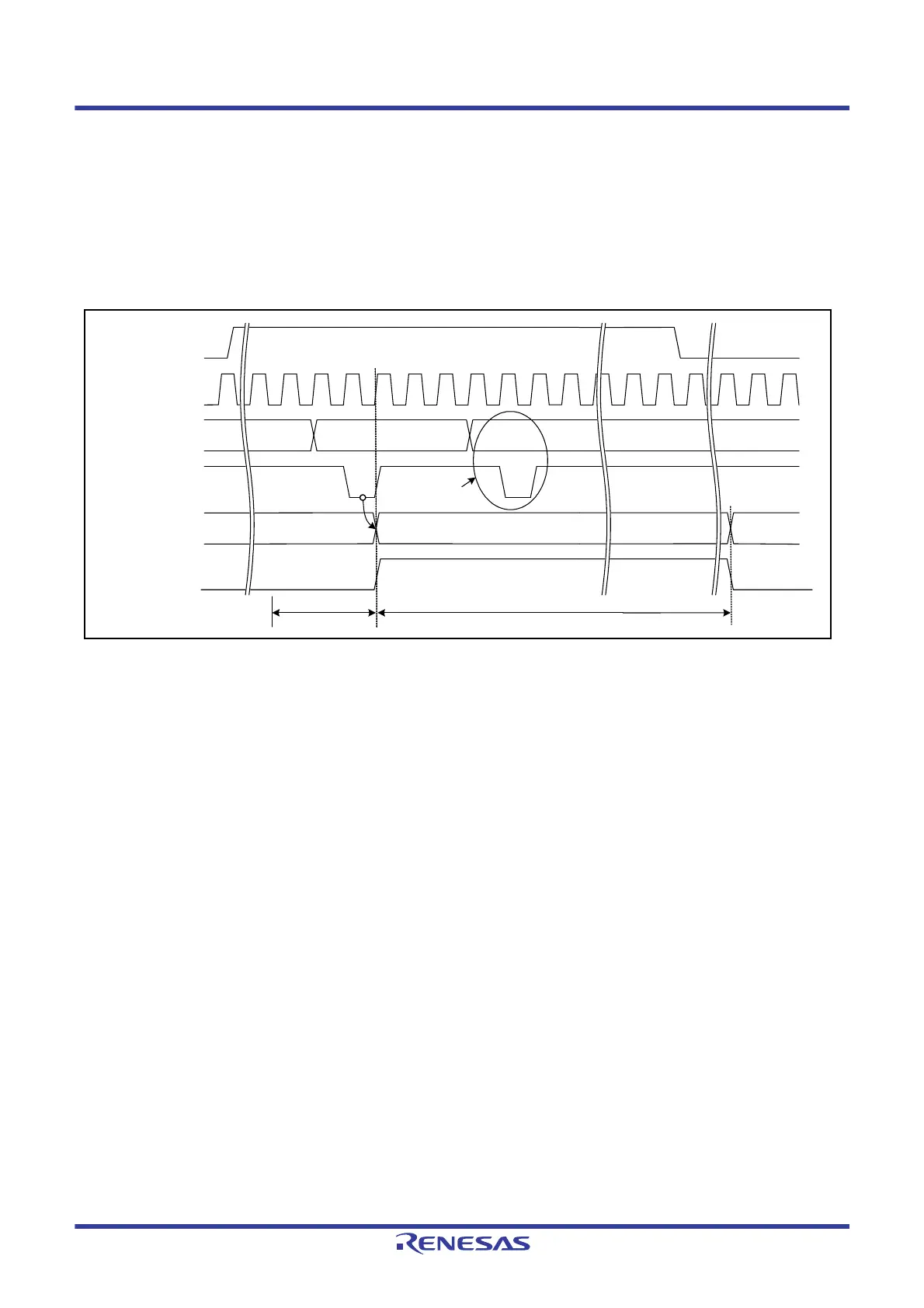

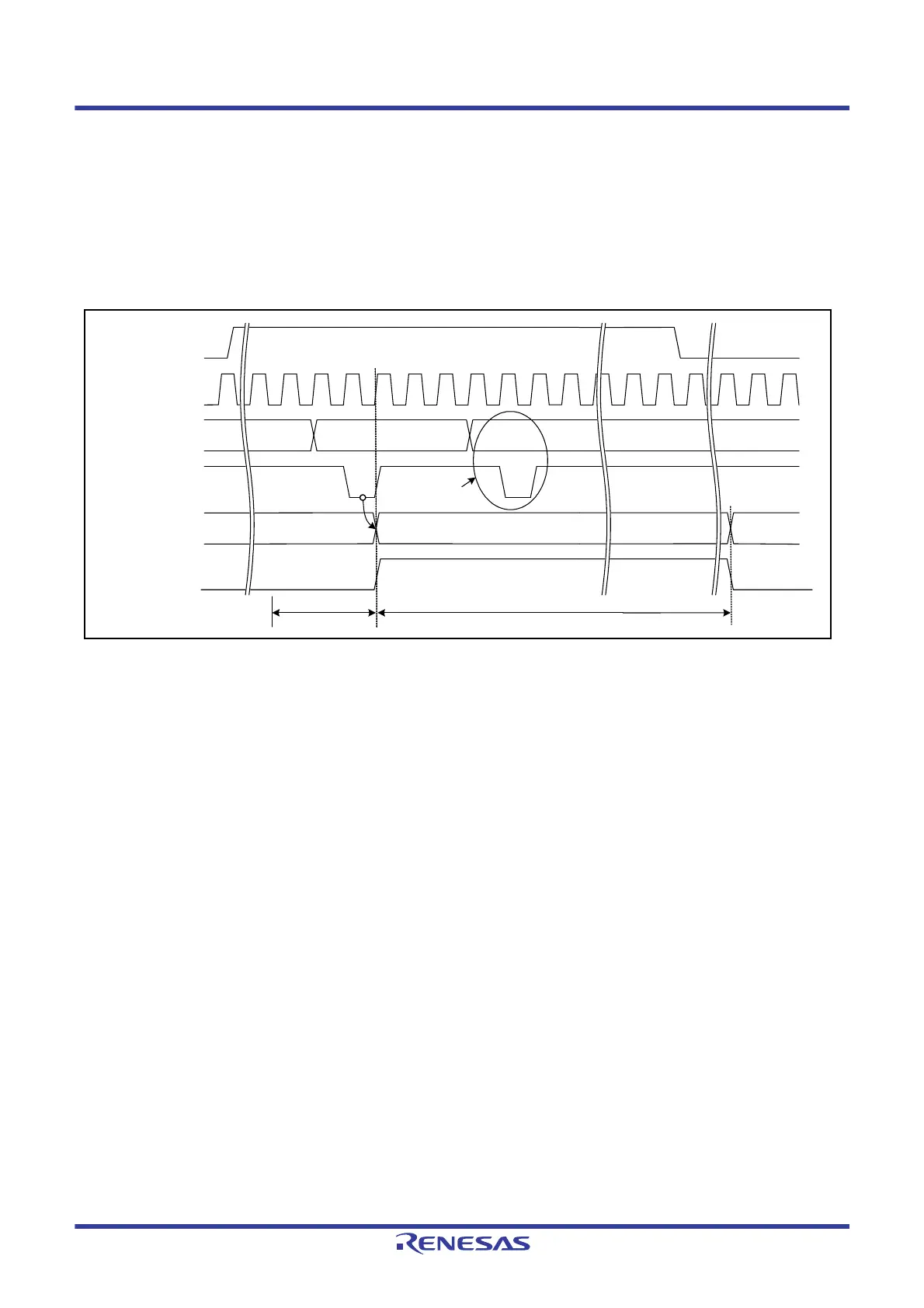

Figure 30.5 shows control waveforms produced in response to writing to the WDTCR register.

Figure 30.5 Control Waveforms Produced in Response to Writing to the WDTCR Register

30.3.3 Refresh Operation

The down-counter is refreshed by writing the values 00h and then FFh to the WDTRR register. If a value other than FFh

is written after 00h, the down-counter is not refreshed. After such invalid writing, correct refreshing is performed by

again writing to 00h and then FFh to the WDTRR register.

Even if a register other than the WDTRR register is accessed or the WDTRR register is read between writing 00h and

writing FFh to the WDTRR register, correct refreshing will be done.

Writing to refresh the counter must be performed within the refresh-permitted period. Whether writing is done within the

refresh-permitted period is determined when writing FFh. For this reason, correct refreshing will be done even if 00h is

written outside the refresh-permitted period.

[Sample sequences of writing that are valid for refreshing the counter]

00h → FFh

00h (n–1-th time) → 00h (nth time) → FFh

00h → access to another register or read from the WDTRR register → FFh

[Sample sequences of writing that are not valid for refreshing the counter]

23h (a value other than 00h) → FFh

00h → 54h (a value other than FFh)

00h→ AAh (00h and a value other than FFh) → FFh

3300h

WDTCR register is protected

(writing-disabled period)

RES# pin

Peripheral module clock

(PCLK)

Data written to WDTCR

register

WDTCR register write

signal (internal signal)

WDTCR register

Register

protection signal

(internal signal)

xxxxh 00F3h

00F3h33F3h (initial value)

Writing disabled

Writing is possible

00F3h 33F3h (initial value)

Loading...

Loading...